影响逻辑分析仪的正常使用的问题。针对上述提出的问题,在原有的逻辑分析仪基础上进行创新设计。技术实现要素:解决的技术问题针对现有技术的不足,本实用新型提供了一种便于散热通风的逻辑分析仪,解决了现有的部分逻辑分析仪常放置于机房内或工作室内,且逻辑分析仪处于相对封闭的状态,使得逻辑分析仪内部的组件在工作中产生的热量无法很好地排出,导致逻辑分析仪内部温度较高,影响逻辑分析仪的正常使用的问题。技术方案为实现上述目的,本实用新型提供如下技术方案:一种便于散热通风的逻辑分析仪,包括逻辑分析仪本体欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。SMI(MDIO)协议分析仪/训练器找欧奥!温州UFS分析仪售价

的发生时间。当需要象接收芯片一样基于时钟边沿,捕获总线中的信息时。接收芯片基于时钟边沿判断总线上的地址、命令和数据。逻辑分析仪象一个侦听器。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。捕获总线上传输的这些信息,并把需要的信息存入存储器。可设置触发条件。捕获需要关注的或出问题的总线上的信息,据此可了解协议或软件执行的情况。上面已经简短讨论了逻辑分析仪的一些用法,现在,让我们更详细地了解一下有关逻辑分析仪的概念。到目前为止,我们已经很地使用了“逻辑分析仪”这一术语。实际上,多数逻辑分析仪中都包含两个分析仪。1.定时分析仪:定时分析仪是逻辑分析仪的一部分,它与示波器相似。事实上。福州UFS分析仪那家好ONFI v4协议分析仪/训练器找欧奥!

将内存深度设置为值的一半(或更小)将返回Pod。在状态采样模式中,在选择了高速状态模式采样选项的情况下,会将一个Pod对保留用于时间标签存储。在定时采样模式中,在选择了跳变/存储限定定时模式采样选项的情况下:选择了小采样周期时,会将一个Pod对保留用于时间标签存储。选择了除小采样周期之外的采样周期时,选择采集内存深度需要将一个Pod对保留用于时间标签存储。在这种情况下,将内存深度设置为值的一半(或更小)将返回Pod。该模块是已分离的逻辑分析仪的一部分。在这种情况下,Pod位于分离分析仪的另一半模块中。状态模式和跳变定时模式下通道数、内存深度和触发之间的相互影响:状态采样模式时,时间标签存储需要1个Pod或1/2的采集内存。在操作界面应用程序中,所有模块都与时间相关;不能关闭timetagstorage(时间标签存储)(虽然以前的Agilent逻辑分析系统可以)。要使用1/2以上的模块采集内存,必须将一个Pod保留用于时间标签存储。要使用所有Pod,内存使用量不能超过模块采集内存的1/2。一般来说,可用定时器数与那些不属于为时间标签存储而保留的Pod数相同。默认设置:时间标签存储始终处于开启状态(并且不能将其关闭)。

我们可以看到时间上的细节。状态分析速率在状态分析时,逻辑分析仪采样基准时钟就用被测试对象的工作时钟(逻辑分析仪的外部时钟)这个时钟的高速率就是逻辑分析仪的高状态分析速率。也就是说,该逻辑分析仪可以分析的系统快的工作频率。主流产品的定时分析速率在300MHz,高可高达500MHz甚至更高。每通道的记录长度逻辑分析仪的内存是用于存储它所采样的数据,以用于对比、分析、转换(譬如将其所捕捉到的信号转换成非二进制信号【汇编语言、C语言、C++等】。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。等在选择内存长度时的基准是"于我们即将观测的系统可以进行分割后的块的长度。PCle Gen 3协议分析仪/训练器找欧奥!

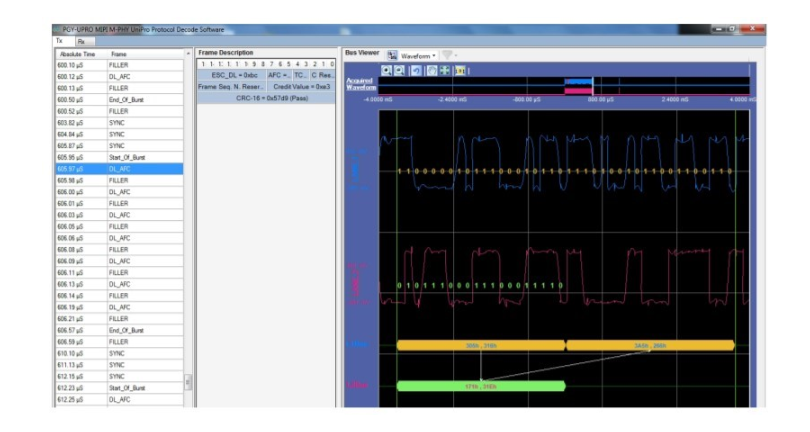

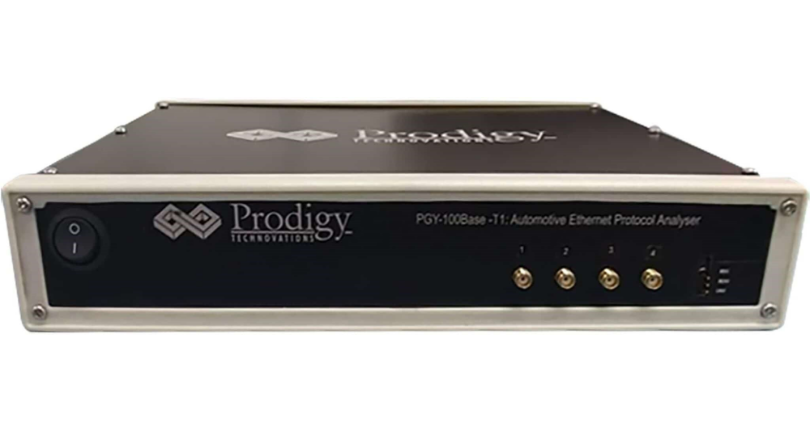

会将一个Pod对保留用于时间标签存储。选择了除小采样周期之外的采样周期时,选择采集内存深度需要将一个Pod对保留用于时间标签存储。在这种情况下,将内存深度设置为值的一半(或更小)将返回Pod。该模块是已分离的逻辑分析仪的一部分。在这种情况下,Pod位于分离分析仪的另一半模块中。状态模式和跳变定时模式下通道数、内存深度和触发之间的相互影响:状态采样模式时,时间标签存储需要1个Pod或1/2的采集内存。在操作界面应用程序中,所有模块都与时间相关;不能关闭timetagstorage(时间标签存储)(虽然以前的Agilent逻辑分析系统可以)。要使用1/2以上的模块采集内存,必须将一个Pod保留用于时间标签存储。要使用所有Pod,内存使用量不能超过模块采集内存的1/2。一般来说,可用定时器数与那些不属于为时间标签存储而保留的Pod数相同。默认设置:时间标签存储始终处于开启状态(并且不能将其关闭)。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器。100BaseTl (Automotive)协议分析仪/训练器找欧奥!杭州EMMC分析仪报价

UniPro协议分析仪/训练器找欧奥!温州UFS分析仪售价

才能符合此表达式。换句话说,在ADDR等于1000的同时DATA等于2000。因此,如果要在同时发生两个事件时触发,则应使用布尔逻辑表达式。常见错误是应使用布尔逻辑表达式时尝试使用两个序列步骤,或者应使用两个序列步骤时尝试使用布尔逻辑表达式。当多个事件同时发生时使用布尔逻辑表达式,而在一个事件接着一个事件发生时使用多个序列步骤。分支:分支类似于C编程语言中的Switch语句和Basic中的SelectCase语句。分支可提供测试多个sADDR”。多数逻辑分析仪还支持“notinrange”功能。范围是一种方便的快捷方式,因此您无需指定“ADDR>=1000andADDR<=>标志:标志是用于从一个模块向另一个模块发送信号的布尔变量。当某种情况在某一模块中发生而稍后被另一模块测试时可以设置标志。在下面的示例中,标志1用于跟踪在模块1的触发序列中发生的情况,如,如果想在ADDR=1000第5次出现时触发,可以将触发设置为:IfADDR=1000occurs5timesthenTrigger全局计数器类似于整数变量。全局计数器比发生计数器更灵活,因为它们可用于为复杂事件(例如一个时钟沿后跟另一时钟沿的事件)计数。可以增加、测试和重新设置全局计数器。默认情况下,全局计数器以零开头并且不需要重新设置。温州UFS分析仪售价

高速存储芯片(UFS、eMMC、Nand Flash)研发对信号完整性、协议合规性、传输稳定性要求严...

【详情】高速信号接口如 UFS、DDR3/DDR4、USB Type-C 等调试难度极高,信号反射、串扰、时...

【详情】高校、科研院所开展芯片设计、接口技术、协议研究时,需要高精度多功能测试平台,但常受预算、工具、支持不...

【详情】航空航天与高级装备研发对硬件安全性、可靠性、一致性要求极高,总线测试需满足严苛规范,普通设备精度不足...

【详情】存储芯片协议分析仪是面向存储芯片研发的专门测试仪器,欧奥电子代理的多款存储芯片协议分析仪,涵盖 UF...

【详情】随着 AI 芯片、大模型终端、智能硬件快速发展,UFS 4.0、HBM、PCIe 5.0、I3C 等...

【详情】嵌入式与汽车电子开发时,I2C、SPI、UART 等低速接口易出现电气不兼容、通信卡顿、时序偏移等问...

【详情】