- 品牌

- 亿芯智研

- 服务项目

- 电子产品仪器设备硬件开发

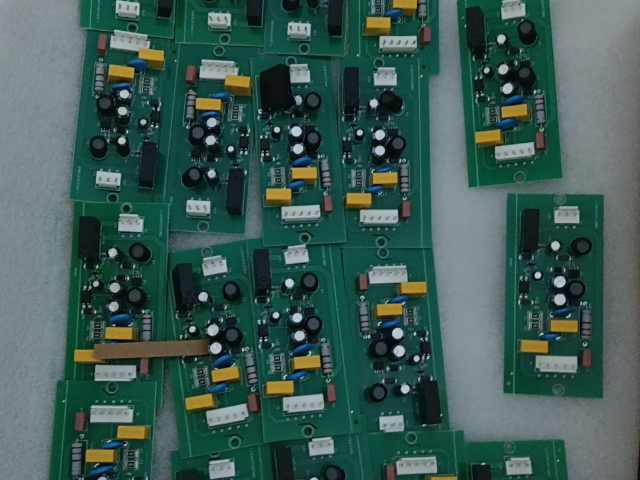

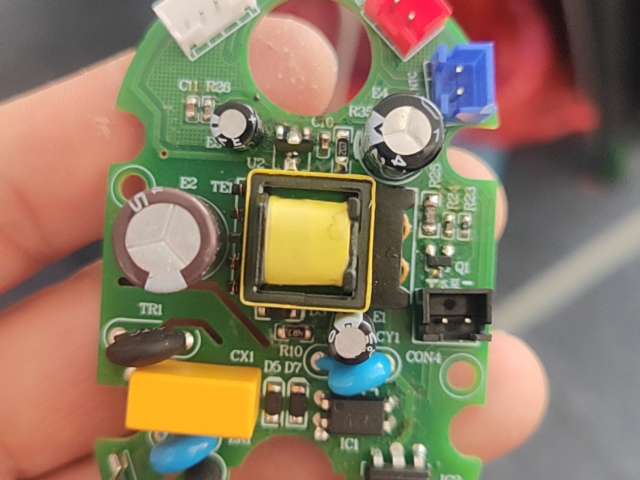

硬件开发和软件开发的顺序并不是固定不变的,它取决于具体的项目需求、技术栈以及开发团队的偏好和流程。然而,在一般情况下,硬件开发和软件开发可以遵循以下顺序进行,但请注意,这个过程可能会根据实际情况有所调整或并行进行。1.需求分析与规划阶段共同参与:在这一阶段,硬件和软件团队都需要与客户或项目发起人紧密合作,共同明确项目需求、功能要求、性能指标等。2.设计与规划阶段硬件设计:总体方案设计:根据需求分析结果,设计硬件的总体方案,包括处理器选型、接口设计、电源方案等。3.开发阶段硬件开发:样板制作:根据设计图纸制作硬件样板,进行初步测试和调试。生产成品板:根据测试结果和调试结果,修改设计图纸,制作生产板,并进行测试和调试。软件开发:编码实现:根据软件设计文档,编写程序代码,实现软件功能。4.集成与测试阶段软硬件集成:将开发完成的硬件和软件集成在一起,进行系统测试和调试。测试:进行功能测试、性能测试、压力测试、安全测试等,确保系统符合需求规格说明书中的要求。5.部署与维护阶段部署:将软件部署到硬件平台上,进行系统配置和用户培训等工作。设计电源电路之前,要对系统中各器件所需电源的需求情况进行分析。嵌入式硬件开发交期

硬件开发

FPGA的力量:2024年AI计算领域的新势力?更多的AI应用将采用FPGA进行加速:随着FPGA技术的成熟和普及,越来越多的AI应用将采用FPGA进行加速。这不*包括云端的大型AI应用,也包括边缘计算和嵌入式系统中的小型AI应用。FPGA与CPU、GPU的协同工作将更加普遍:在未来的AI计算体系中,是与CPU、GPU等传统处理器紧密协同工作的一部分。通过合理的任务划分和调度,可以充分发挥各种处理器的优势,提高整个系统的性能和能效比。FPGA编程工具和生态将更加完善:为了方便用户开发和部署基于FPGA的AI应用,未来的FPGA编程工具和生态将更加完善。这将包括更易用的编程语言、更高效的编译工具、更丰富的库函数和更完善的社区支持等。定制化FPGA将成为趋势:随着AI应用的多样化和复杂化,未来的FPGA可能不再是通用的标准产品,而是根据具体应用需求定制的专属产品。这将要求FPGA厂商具备更强的定制化能力和更灵活的生产流程。新的FPGA架构和技术将不断涌现:为了适应AI计算的需求和挑战,未来的FPGA架构和技术将不断创新和发展。这可能包括更高效的逻辑块设计、更灵活的互连资源配置、更低功耗的工作模式等。 江苏光伏硬件开发需要多长时间随着科技的不断发展,硬件开发将继续发挥重要作用,推动各个领域的进步和改善。

手术机器人,医学上常称为“达·芬奇机器人外科手术系统”,是一种替代腹腔镜及胸腔镜的“主仆控制式”内镜显微手术系统。其工作原理融合了多个学科的技术,包括医学、材料学、自动控制学、数字图像处理学、生物力学以及机器人学等,是一个多学科高度集成的综合体。以下是手术机器人工作原理的详细阐述:一、系统组成手术机器人系统主要由以下几部分组成:主机控制系统,传输和支持系统,影像输出系统。二、工作原理精细操控:手术机器人通过其高精度的机械臂和手术器械,实现了对手术操作的精细控制。机械臂模拟了人类手臂的灵活性和精确度,同时过滤了人手本身的震颤,从而提高了手术的稳定性和安全性。实时反馈:传输和支持系统确保了手术过程中信息的实时反馈。

FPGA(Field-ProgrammableGateArray,现场可编程门阵列)硬件设计是一个复杂但高度灵活的过程,它允许工程师通过编程来配置FPGA芯片以实现特定的数字电路功能。以下是对FPGA硬件设计流程的详细解析:一、FPGA硬件设计流程概述FPGA硬件设计流程主要包括以下几个关键步骤:需求分析、FPGA芯片选择、硬件框图设计、HDL编程、仿真测试、布局布线、配置与调试。二、具体步骤详解需求分析确定FPGA的应用需求,包括功能需求、性能需求、成本预算等。根据需求确定FPGA板卡的尺寸、工作频率、IO口数量、运行环境等设计规格。三、FPGA硬件设计工具在FPGA硬件设计过程中,需要使用一系列工具来辅助完成各个步骤。这些工具通常包括:IDE(集成开发环境):如Xilinx的Vivado和Intel的QuartusPrime,它们集成了代码编辑、综合、仿真和调试等功能,能够提高设计效率。HDL编辑器:用于编写和编辑HDL代码。仿真工具:如ModelSim,用于对HDL代码进行功能仿真和时序仿真。布局布线工具:负责将HDL代码翻译成物理电路图,并进行布局和布线。四、FPGA硬件设计的优势FPGA硬件设计具有以下几个优势:灵活性:FPGA可以通过编程来配置不同的电路功能,具有很高的灵活性。 硬件设计中原理图和PCB设计都有对应的工具,教程也很多,且比较容易上手。

硬件开发的难点主要体现在多个方面,这些难点不仅考验着开发者的技能,还涉及到项目管理、团队协作、技术创新等多个层面。以下是一些主要的难点:1.设计与实现复杂性高:硬件产品的设计需要考虑众多因素,如功能需求、性能指标、降低成本、可制造性等,这些都需要开发者具备深厚的知识和丰富的实践经验。2.供应链管理多供应商协调:硬件产品的生产往往涉及多个供应商和制造商,如何管理供应链,确保原材料和零部件的质量、交期和成本,是开发者需要面对的重要问题。3.质量制定标准:硬件产品的质量直接关系到用户的使用体验和企业的声誉,因此,开发者需要制定严格的质量标准和测试流程,确保产品的各项指标符合要求。4.降低成本成本构成复杂:硬件产品的成本包括原材料成本、制造成本、研发成本等多个方面,如何在保证产品质量的同时,合理降低成本成本,是开发者需要权衡的问题。 硬件开发工程师必须具备的技能有哪些?嵌入式硬件开发交期

硬件不会像软件一样代码错了修改一下几分钟就搞定,硬件设计错了,那可能要重来,整个周期就要延迟。嵌入式硬件开发交期

设计PCB时使用蛇形走线(也被称为蛇行、蜿蜒或曲折布线)是出于多种考虑,主要包括以下几个方面:一、信号完整性减少信号反射和串扰:在高速电子设备中,信号完整性至关重要。蛇形走线通过增加信号线的物理长度和改变其形状,有助于减少信号的反射和串扰,二、时延匹配同步信号:对于差分信号或同步信号,时延匹配至关重要。蛇形走线可以更容易地实现时延匹配,确保信号同时到达目的地,从而维持系统的时序准确性。三、电磁兼容性(EMC)减少电磁干扰(EMI):蛇形走线可以减少回流路径的长度,降低电流回流时产生的电磁场,从而减少辐射和敏感信号的干扰。四、空间利用和布局优化填充空白区域:PCB布局中常常存在一些不规则的空白区域,无法容纳直线走线。五、特殊应用代替保险丝提供过载保护:蛇形走线通过特定的设计可以限制通过它的电流,从而起到类似保险丝的保护作用。但这种方法可靠性可能较低,需谨慎使用。 嵌入式硬件开发交期

FPGA的力量:2024年AI计算领域的新势力?更多的AI应用将采用FPGA进行加速:随着FPGA技术的成熟和普及,越来越多的AI应用将采用FPGA进行加速。这不*包括云端的大型AI应用,也包括边缘计算和嵌入式系统中的小型AI应用。FPGA与CPU、GPU的协同工作将更加普遍:在未来的AI计算体系中,是与CPU、GPU等传统处理器紧密协同工作的一部分。通过合理的任务划分和调度,可以充分发挥各种处理器的优势,提高整个系统的性能和能效比。FPGA编程工具和生态将更加完善:为了方便用户开发和部署基于FPGA的AI应用,未来的FPGA编程工具和生态将更加完善。这将包括更易用的编程语言、更高...

- 上海医疗设备硬件开发环境 2024-12-04

- 浙江电力设备硬件开发价格 2024-12-04

- 北京分析仪器设备硬件开发制作 2024-12-04

- 内蒙古智能设备硬件开发平均价格 2024-12-04

- 福建电子科技产品硬件开发源码交付 2024-12-04

- 江西储能设备硬件开发公司 2024-12-04

- 江西电子科技产品硬件开发功能 2024-12-04

- 光伏硬件开发制作 2024-12-04

- 汽车新能源硬件开发需要多长时间 2024-12-03

- 硬件开发有哪些公司 2024-12-03

- 分析仪器设备硬件开发设计 2024-12-03

- 内蒙古智能设备硬件开发公司 2024-12-03

- 山东分析仪器设备硬件开发调试 2024-12-03

- 北京电力设备硬件开发调试 2024-12-03

- 江苏光伏硬件开发测试 2024-12-02

- 北京医疗设备硬件开发交期 2024-12-02

- 福建电子科技产品硬件开发源码交付 12-04

- 江西储能设备硬件开发公司 12-04

- 江西电子科技产品硬件开发功能 12-04

- 光伏硬件开发制作 12-04

- 汽车新能源硬件开发需要多长时间 12-03

- 硬件开发有哪些公司 12-03

- 浙江储能设备硬件开发注意事项 12-03

- 北京汽车新能源硬件开发需求 12-03

- 福建数据采集器硬件开发服务 12-03

- 安徽检测仪器设备硬件开发测试 12-03