UFS 信号完整性测试之维修中的信号检测

设备维修时,UFS 信号完整性检测可快速定位故障。若设备频繁死机,可检测 UFS 信号是否存在反射、串扰。用简易示波器测量信号波形,与正常波形比对。若信号失真严重,可能是接口氧化、线路损坏等。通过信号检测,能缩小故障范围,提高维修效率,减少盲目更换元件的成本,让设备尽快恢复正常运行。

UFS 信号完整性测试之芯片级测试与板级测试区别

UFS 芯片级测试与板级测试有明显区别。芯片级测试在芯片出厂前进行,关注芯片内部信号传输,需高精度探针台配合。板级测试针对 PCB 板上的 UFS 模块,侧重线路、接口对信号的影响。芯片级测试确保芯片本身性能,板级测试评估系统集成后的信号质量。二者相辅相成,共同保障 UFS 从芯片到整机的信号完整性。 UFS 信号完整性测试之信号完整性与产品质量?测试原理UFS信号完整性测试克劳德

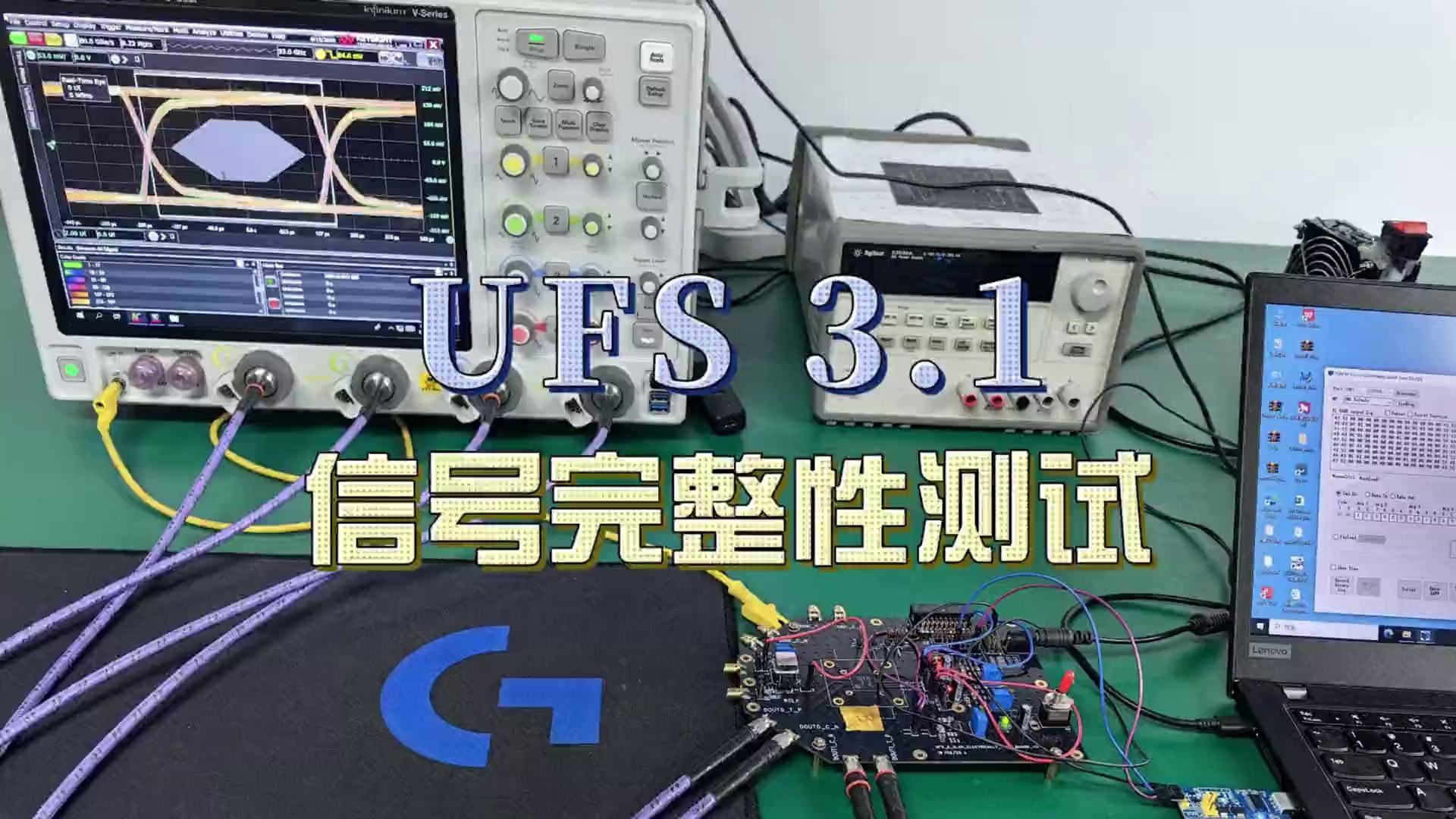

UFS信号完整性测试

UFS 信号完整性测试之共模干扰抑制

UFS 采用差分信号技术抑制共模干扰,保障信号完整性。差分信号由两个幅度相等、相位相反信号组成。共模干扰同时影响这两个信号,接收端通过比较二者差值,消除共模干扰影响。在测试中,要检查差分信号传输路径是否合理,防止外界干扰破坏差分信号特性。抑制共模干扰,能提升 UFS 信号抗干扰能力,让信号在复杂电磁环境下,仍保持完整性,稳定传输数据。

UFS 信号完整性测试之信号失真排查

信号失真会严重影响 UFS 信号完整性。电磁干扰、反射、串扰等都能导致信号失真。测试时,通过观察信号波形、分析频谱等方法排查失真原因。若因电磁干扰,可增加屏蔽措施;若是反射问题,优化线路阻抗匹配;串扰则调整信号间距。及时发现并解决信号失真问题,能让 UFS 信号保持清晰、准确,确保设备存储与传输数据的稳定性。 软件测试UFS信号完整性测试检测报告UFS 信号完整性测试之测试数据解读技巧?

UFS 硬件架构与信号完整性关联

UFS 硬件架构设计影响信号完整性。差分对下方要保留连续地平面,防止跨分割,避免信号反射。接收端添加 100Ω 差分端接电阻(集成于主控或外置),能匹配阻抗,减少信号失真。相邻信号对间距≥3 倍线宽,并用地屏蔽过孔(Guard Via),可抑制串扰。合理规划硬件架构,为信号完整性提供物理基础,确保 UFS 数据高速、准确传输,让设备发挥比较好性能。

UFS 信号完整性测试之信号质量优

化优化 UFS 信号质量是信号完整性测试的目的之一。优化信号上升 / 下降时间,能让信号更清晰,减少码间干扰。借助信号完整性分析工具,如 Ansys HFSS 进行仿真,可提前优化布线策略。在设计阶段,注重阻抗控制,保证传输线阻抗匹配,减少信号反射。良好的信号质量是 UFS 数据可靠传输的保障,能提升设备存储与读取数据的效率。

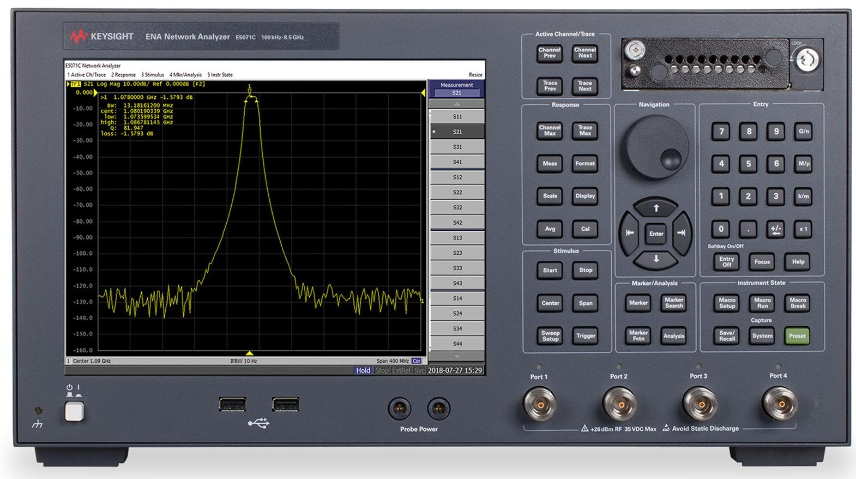

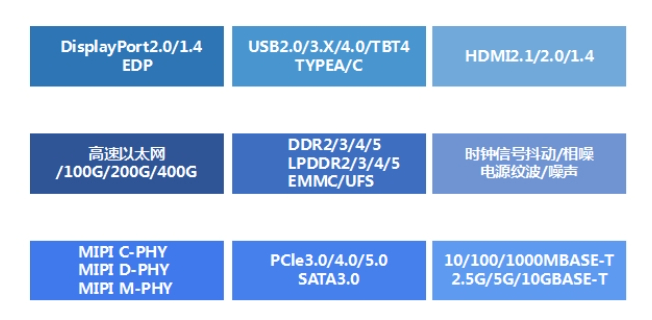

UFS信号完整性基础概念UFS信号完整性测试是验证高速串行接口性能的关键环节,主要评估信号在传输过程中的质量衰减。测试频率覆盖1.5GHz至11.6GHz(UFS3.1标准),重点关注差分信号的幅度、时序和噪声特性。典型测试参数包括眼图高度/宽度、抖动、插入损耗等,需满足JEDECJESD220C规范要求。MIPIM-PHY物理层测试UFS采用MIPIM-PHY作为物理层接口,测试需关注HS-Gear3/4模式下的信号特性。关键指标:差分幅度200-400mVpp,共模电压0.9-1.2V,上升时间<35ps。测试需使用16GHz以上带宽示波器,通过TDR验证阻抗匹配(100Ω±10%)。UniPro协议层验证除物理层外,还需验证UniPro协议层的信号完整性。测试内容包括:链路训练过程信号稳定性、LCC(Lane-to-LaneCalibration)后的时序一致性、电源状态切换时的信号恢复时间。建议采用协议分析仪捕获L1-L4状态转换波形。眼图测试方法论UFS眼图测试需累积≥1E6比特数据,评估标准:垂直开口≥70mV,水平开口≥0.6UI。需区分随机抖动(RJ)和确定性抖动(DJ),其中RJ应<1.5psRMS。测试时建议关闭均衡功能以评估原始信号质量。UFS 信号完整性测试之预编码和调制技术作用?

UFS 信号完整性测试之 5G 通信协同

5G 通信的高速率、低延迟需求与 UFS 信号完整性紧密相关。5G 基站和终端设备中,UFS 用于存储大量数据,其信号稳定性影响数据处理速度。当 5G 网络传输数据到 UFS 存储设备时,若信号完整性差,数据存储可能出错,导致通信中断或延迟增大。测试时,需结合 5G 通信特点,模拟高速数据传输场景。优化 UFS 与 5G 通信模块的接口设计,降低信号传输损耗。保障 UFS 信号完整性,能实现与 5G 通信协同工作,提升 5G 网络整体性能,为用户带来更好通信体验。 UFS 信号完整性之抖动测试?数字接口测试系列UFS信号完整性测试抖动测试

UFS 信号完整性测试之接口设计要点?测试原理UFS信号完整性测试克劳德

UFS 信号完整性测试之信号完整性与功耗关系

UFS 信号完整性与功耗存在关联。减少信号摆幅可降低功耗,但可能信号信噪比,影响信号完整性。在设计与测试中,需平衡二者关系。例如,在满足信号完整性前提下,优化信号电平,降低功耗。通过合理选择电路元件、优化线路设计,既能保证信号可靠传输,又能降低设备功耗,提升 UFS 设备整体性能与续航能力。

UFS 信号完整性测试之信号完整性与传输速率

UFS 传输速率越高,对信号完整性要求越高。高速传输时,信号更容易受干扰、发生失真。在 UFS 4.0 中,M-PHY 5.0 速率达 12Gbps / 通道 ,信号完整性挑战巨大。通过优化线路布局、采用先进信号处理技术,保障信号完整性,才能实现高速率数据传输。信号完整性是 UFS 提升传输速率的保障,二者相辅相成,共同推动 UFS 性能进步。 测试原理UFS信号完整性测试克劳德

UFS信号完整性测试的重要性UFS(通用闪存存储)作为高速存储接口,其信号完整性直接影响数据传输的稳定性和可靠性。随着UFS3.1/4.0速率提升至23.2Gbps,微小的信号失真即可导致严重的误码问题。信号完整性测试能确保关键参数(如眼图、抖动、阻抗匹配)符合JEDEC和MIPI标准,避免因信号劣化引发系统故障或数据错误。在研发阶段,SI测试可快速定位设计缺陷(如走线过长、阻抗失配),优化PCB布局,降低后期改版风险。量产阶段则通过统计测试确保生产一致性,提升产品良率。此外,严苛环境测试(如高温、振动)能验证产品的长期可靠性。随着5G、AI等应用对存储性能要求不断提高,完善的UFS信号完...

- 数字接口测试系列UFS信号完整性测试多端口矩阵测试 2026-04-08

- 转接板UFS信号完整性测试克劳德高速数字信号测试实验室 2026-04-07

- 克劳德实验室UFS信号完整性测试检测 2026-04-06

- 仪器仪表测试UFS信号完整性测试信号完整性测试 2026-04-06

- 信息化UFS信号完整性测试兼容性测试 2026-04-06

- 校准UFS信号完整性测试执行标准 2026-04-06

- 信息化UFS信号完整性测试阻抗测试/TDR测试/回波损耗测试 2026-04-06

- 高速接口UFS信号完整性测试项目 2026-04-06

- 测试项目介绍UFS信号完整性测试物理层测试 2026-04-05

- 自动化UFS信号完整性测试信号完整性测试 2026-04-05

- 数字接口测试系列UFS信号完整性测试方案商 2026-04-05

- 数字接口测试系列UFS信号完整性测试高速信号传输 2026-04-05

- UFS信号完整性测试兼容性测试 2026-04-04

- 设备UFS信号完整性测试检测 2026-04-04

- 测量UFS信号完整性测试项目 2026-04-04

- 软件测试UFS信号完整性测试信号眼图 2026-04-04

- 数字信号信号完整性测试维保 04-09

- 眼图测试UFS信号完整性测试检测 04-08

- 广东校准PCIE3.0TX一致性测试联系方式 04-08

- 数字信号SATA测试一致性测试 04-08

- 解决方案LVDS发射端一致性测试检查 04-08

- 数字接口测试系列UFS信号完整性测试多端口矩阵测试 04-08

- 智能化多端口矩阵测试信号完整性测试规格尺寸 04-08

- 江苏信息化以太网1000M物理层测试 04-08

- 机械信号完整性测试销售 04-08

- HDMI测试信号完整性测试HDMI测试 04-08