- 品牌

- 华昕

- 型号

- 晶振全品类

- 频率特性

- 高频,低频

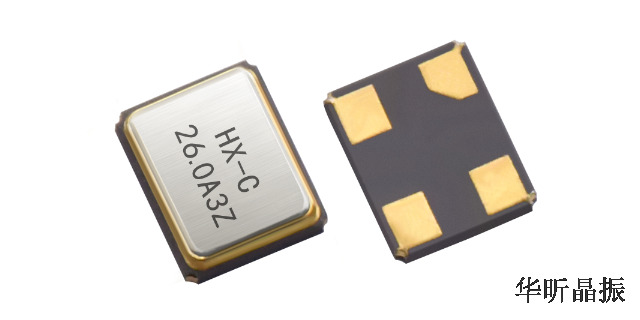

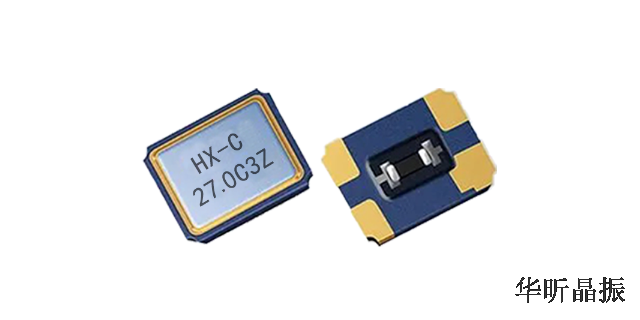

- 封装材料

- 金属,陶瓷

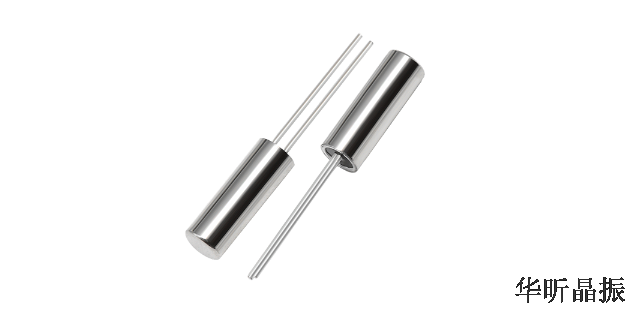

- 外形

- 贴片式,直插式

- 标称频率

- 1~200

- 调整频差

- 1~200

- 基准温度

- -40~+85

- 负载电容

- 6pf~20pf

- 静态电容

- 3

- 老化率

- 2

- 温度范围

- -40~+85

- 产地

- 中国

- 厂家

- 华昕

- 封装尺寸

- 1612/2016/2520/3225/5032/7050

晶振的制造过程主要包括以下几个关键步骤:原材料准备:晶振的关键组件是石英晶片,首先需要准备原始的石英晶体材料。晶片切割:将选取好的石英材料进行高精度的切割,以得到符合设计要求的晶片。这一步骤需要严格控制晶片的尺寸、形状和厚度等参数。清洗与镀膜:在制造过程中,晶片需要进行清洗以去除表面的杂质。随后,采用溅射或其他方法在晶片表面镀膜,通常是金属薄膜如银,以形成电极。电极制作:在晶片的两面制作电极,电极用于施加电压以激发石英晶体的压电效应。点胶与烘胶:在晶片的特定位置上涂抹胶水,以固定晶片和其他组件的连接。然后,将点胶后的晶片进行烘烤,以加快胶水的固化和固定连接。频率微调:调整晶振的振荡频率,使其达到设计要求。这一步骤可能需要多次迭代以获得比较好频率。封装:将制作好的晶片放置在适当的封装材料中,以保护晶片并提供机械支撑。封装过程中需要确保晶片与封装材料之间的热膨胀系数匹配,以防止温度变化引起的应力损伤。以上步骤完成后,晶振就制造完成了。不可缺少的晶振,晶振概述。stm32外接晶振

晶振的启动时间是指从通电到晶振开始稳定振荡所需的时间,这个时间一般很短,通常在几毫秒到几秒之间,取决于晶振的类型、频率和外部电路等因素。晶振的启动时间对电路启动有重要影响。在一些对实时性要求较高的应用中,电路需要在短时间内启动并开始工作,因此晶振的启动时间必须足够短,以确保电路能够迅速进入正常工作状态。如果晶振的启动时间过长,可能会导致电路启动失败或无法满足实时性要求。此外,晶振的启动时间还与电路的稳定性有关。如果晶振在启动过程中受到干扰或发生故障,可能会导致电路无法正常工作或产生不稳定的现象。因此,在选择晶振时,需要考虑其启动时间以及稳定性等参数,以确保电路能够稳定可靠地工作。在实际应用中,为了降低晶振的启动时间并提高电路的稳定性,可以采取一些措施,如优化电路设计、选择合适的晶振类型和频率、调整外部电路参数等。这些措施有助于提高电路的性能和可靠性,使其能够满足各种应用需求。石英晶振 晶体管晶振的技术指标与晶振的等效电气特性。

晶振的抗干扰能力是其性能评估中的一个重要指标。通常情况下,晶振具有较强的抗干扰能力,这主要得益于其设计和制造过程中的一系列优化措施。首先,晶振的抗干扰能力与其内部结构和材料密切相关。高质量的晶振采用质量的晶体材料和先进的制造工艺,确保其在工作时能够抵抗来自外部环境的干扰,如电磁干扰、温度变化等。其次,晶振的抗干扰能力还受到其封装形式的影响。一些先进的封装技术,如金属封装和陶瓷封装,能够有效地屏蔽外部电磁干扰,提高晶振的抗干扰能力。此外,晶振的抗干扰能力还与其工作频率和工作温度范围有关。一般来说,较低频率的晶振抗干扰能力较强,而高温环境可能会对晶振的性能产生影响,因此在选择晶振时需要根据实际应用环境进行综合考虑。为了提高晶振的抗干扰能力,制造商通常会采取一系列措施,如优化电路设计、加强封装等。同时,用户在使用晶振时也可以采取一些措施来降低干扰的影响,如合理布局电路、选择适当的电源和接地方式等。总之,晶振的抗干扰能力是其性能的重要组成部分,用户在选择和使用晶振时需要关注其抗干扰能力,并根据实际需求进行综合考虑。

晶振在高频电路中的表现非常关键,因为它提供了电路所需的高频稳定信号。晶振具有高精度和高稳定性,能够在高频环境下持续产生准确的时钟频率,这是保证高频电路正常工作的重要前提。在高频电路中,晶振的启动时间、频率稳定性、相位噪声等参数都至关重要。启动时间短的晶振能够迅速进入稳定工作状态,减少电路启动时的等待时间。频率稳定性好的晶振能够在不同工作环境下保持频率的一致性,确保电路的稳定运行。相位噪声低的晶振能够减少信号失真和干扰,提高电路的性能。此外,晶振在高频电路中还需要考虑其抗冲击和振动能力。由于高频电路往往工作在复杂的环境中,晶振需要能够承受一定的冲击和振动,以确保电路的稳定性和可靠性。总的来说,晶振在高频电路中的表现非常出色,能够提供稳定、准确的高频信号,保证电路的正常工作。然而,在选择晶振时需要根据具体的应用场景和需求进行综合考虑,以确保晶振的性能能够满足电路的要求。如何降低晶振的相位噪声?

晶振的Q值,也称为“品质因数”,是晶振的一个重要电气参数。它表示了周期存储能量与周期损失能量的比值。在石英晶体谐振器中,Q值越大,其频率的稳定度就越高。具体来说,Q值的大小反映了晶振内阻的大小、损耗的大小、需要的激励功率的大小以及起振的难易程度。Q值大,说明晶振内阻小、损耗小、需要的激励功率小、容易起振,晶振稳定性越好。Q值对电路性能的影响主要体现在以下几个方面:频率稳定性:Q值越高,晶振的频率稳定性越好。这是因为Q值大意味着晶振的损耗小,能够更好地维持其振荡频率。起振性能:Q值大的晶振更容易起振。在电路设计中,如果晶振的起振困难,可能会导致电路无法正常工作。因此,选择Q值大的晶振有助于提高电路的起振性能。抗干扰能力:Q值大的晶振具有较好的抗干扰能力。在复杂的电磁环境中,晶振容易受到外界干扰而导致性能下降。Q值大的晶振能够更好地抵御外界干扰,保持其稳定性和准确性。总之,晶振的Q值是衡量其性能的重要指标之一。在电路设计中,选择Q值合适的晶振有助于提高电路的频率稳定性、起振性能和抗干扰能力。晶振的相位噪声是如何定义的?它对电路有何影响?吉林硅晶振

晶振的抗冲击和振动能力如何?stm32外接晶振

晶振的相位噪声在频域上被用来定义数据偏移量。对于频率为f0的时钟信号而言,如果信号上不含抖动,那么信号的所有功率应集中在频率点f0处。然而,由于任何信号都存在抖动,这些抖动有些是随机的,有些是确定的,它们分布于相当广的频带上,因此抖动的出现将使信号功率被扩展到这些频带上。相位噪声就是信号在某一特定频率处的功率分量,将这些分量连接成的曲线就是相位噪声曲线。它通常定义为在某一给定偏移处的dBc/Hz值,其中dBc是以dB为单位的该功率处功率与总功率的比值。例如,一个振荡器在某一偏移频率处的相位噪声可以定义为在该频率处1Hz带宽内的信号功率与信号总功率的比值。相位噪声对电路的影响主要体现在以下几个方面:频率稳定性:相位噪声的增加会导致振荡器的频率稳定性下降,进而影响整个电路的工作稳定性。通信质量:在通信系统中,相位噪声会影响信号的传输质量,增加误码率,降低通信的可靠性。系统性能:相位噪声还会影响电路的其他性能指标,如信噪比、动态范围等,进而影响整个系统的性能。因此,在电路设计中,需要采取一系列措施来降低晶振的相位噪声,以保证电路的稳定性和性能。例如,可以选择低噪声的晶振、优化电路布局、降低电源电压波动等。stm32外接晶振

晶振在微处理器中的应用主要体现在以下几个方面:时钟信号生成:晶振是微处理器中的关键组件之一,负责产生稳定的时钟信号。这个时钟信号是微处理器内部各种操作的基准,包括指令的读取、解码和执行,数据的读取和写入等。同步控制:微处理器内部的各种功能部件需要按照一定的时序进行工作,晶振产生的时钟信号确保了这些部件之间的同步。这有助于防止数据***和时序错误,保证微处理器的正确运行。频率控制:晶振的频率决定了微处理器的时钟频率,进而影响微处理器的性能。通过选择合适的晶振,可以调整微处理器的时钟频率,从而满足不同的应用需求。系统稳定性:晶振的稳定性和精度直接影响微处理器的性能稳定性。高质量的晶振能够提供稳定的...

- 西藏2520晶振 2024-12-12

- 100mhz差分晶振 2024-12-12

- 贴片无源晶振的英文 2024-12-12

- silcon晶振 2024-12-11

- 生产晶振 2024-12-11

- 电子表晶振 2024-12-11

- 晶振2016 2024-12-11

- 鸿星 晶振 2024-12-11

- 8m晶振 3.3v 3225 2024-12-11

- 晶振常用牌子 2024-12-10

- 25m无源晶振并联电容大小 2024-12-09

- 珠海华昕开发建设有限公司 2024-12-09

- 西安24MHZ晶振 2024-12-09

- 深圳创捷电子有限公司 2024-12-09

- 全球晶振供应商 2024-12-08

- 天津静海生产晶振的厂家 2024-12-08

- 厦门无源晶振30MHZ 12-22

- 杭州无源晶振26MHZ 12-22

- 北京无源晶振排名 12-22

- 无锡厂家无源晶振 12-21

- 广州无源晶振频率 12-21

- 圆柱无源晶振生产商 12-21

- 安徽无源晶振27MHZ 12-21

- 4M石英晶振分类 12-20

- 22.1184M石英晶振生产商 12-20

- 石家庄无源晶振厂家 12-20