FPGA开发板的调试是确保设计功能正确的关键环节,常用调试工具和方法包括在线逻辑分析仪、信号探针、软件仿真和硬件断点。在线逻辑分析仪是FPGA开发工具的功能,可通过JTAG接口实时采集FPGA内部信号,设置触发条件,观察信号时序波形,定位逻辑错误,例如检测计数器是否出现跳数、状态机是否进入异常状态。信号探针是在FPGA内部设置的测试点,可将关键信号引到外部引脚,通过示波器观察信号波形,分析时序问题,如信号延迟、抖动是否符合要求。软件仿真是在开发工具中搭建测试平台,输入测试向量,模拟FPGA的逻辑功能,验证代码正确性,适合在硬件调试前排查基础逻辑错误。硬件断点是在FPGA程序中设置断点,当程序运行到断点位置时暂停,查看寄存器和内存数值,分析程序运行状态。调试时需结合多种方法,例如先通过软件仿真验证逻辑功能,再通过在线逻辑分析仪和示波器排查时序问题,提高调试效率。 FPGA 开发板时钟选择电路支持频率切换。山东学习FPGA开发板平台

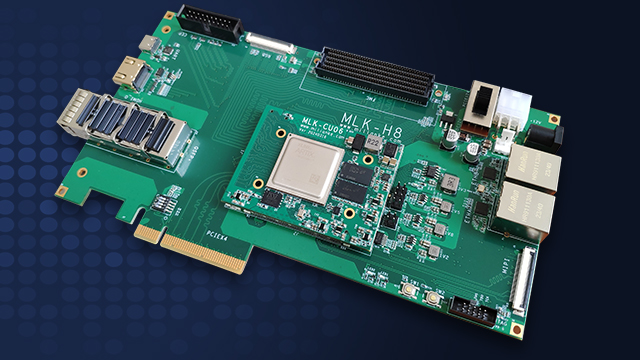

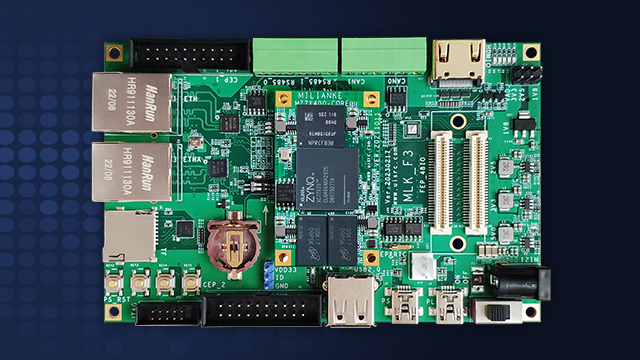

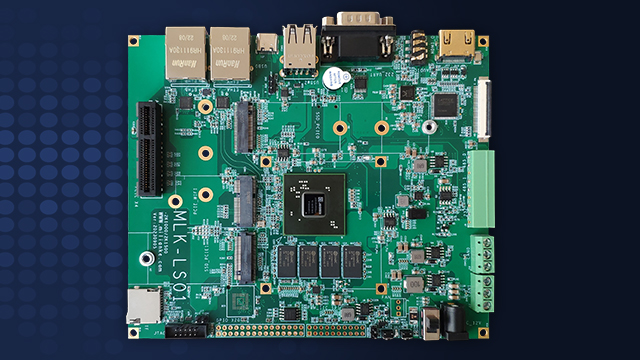

米联客MIZ7035FPGA开发板(Zynq-7035款)面向高性能嵌入式应用,米联客MIZ7035开发板采用XilinxZynq-7035芯片,集成双核ARMCortex-A9处理器(比较高工作频率1GHz)与100万逻辑单元的FPGA资源,具备更强的数据处理与硬件加速能力。硬件配置上,开发板搭载1GBDDR3内存、32GBeMMC闪存,板载HDMI输入/输出双接口、USB接口、SATA接口及PCIeGen2接口,可连接高速存储设备、高清摄像头等外设,满足图像视频处理、高速数据存储等需求。软件支持方面,开发板提供Petalinux高级镜像与Vitis开发工具链,支持OpenCV图像处理库、FFmpeg视频编解码库的移植与使用,用户可开发高清视频采集、图像识别等应用。配套资料包含图像处理案例(如边缘检测、图像缩放)、高速接口通信案例(如PCIe数据传输、SATA存储读写),帮助用户快速上手复杂项目开发。该开发板还具备完善的散热设计,通过金属散热片降低芯片工作温度,保障高负载运行时的稳定性,适合嵌入式高性能计算、智能视觉处理等场景。 吉林工控板FPGA开发板设计FPGA 开发板逻辑分析仪接口支持信号采集。

FPGA开发板在航空航天领域发挥着关键作用。在卫星通信系统中,开发板用于实现卫星与地面站之间的高速数据传输和复杂的信号处理功能。卫星在太空中会接收到大量的遥感数据、通信数据等,FPGA开发板能够对这些数据进行编码、调制,通过卫星通信链路将数据传输至地面站。在地面站接收端,开发板则负责对信号进行解调和数据处理,确保数据的准确接收和解析。同时,由于卫星通信环境复杂,存在各种干扰信号,开发板可利用其灵活的逻辑资源,实现自适应的信号处理算法,提高通信的可靠性。在飞行器的导航系统中,开发板可对惯性导航传感器、卫星导航等设备的数据进行实时采集和处理,结合复杂的导航算法,为飞行器提供精确的位置、速度和姿态信息,提高飞行器在飞行过程中的导航精度和安全性,在航空航天领域的探索和应用中发挥着不可替代的作用。

I2C接口是一种低成本、低速率的串行通信接口,在FPGA开发板中常用于连接EEPROM(电可擦除可编程只读存储器)、传感器、实时时钟(RTC)等外设。其典型架构包括SDA(串行数据线)和SCL(串行时钟线)两根信号线,支持多主多从拓扑结构,通过从机地址区分不同外设。在EEPROM应用中,FPGA可通过I2C接口读取或写入配置信息,如板卡序列号、硬件版本号;在传感器应用中,可通过I2C接口读取温湿度传感器、光照传感器的数据,实现环境监测;在RTC应用中,可通过I2C接口获取实时时间,为系统提供时间戳。I2C接口的传输速率较低,通常为100kbps(标准模式)或400kbps(快速模式),适合对传输速率要求不高的场景,但布线简单,只需两根信号线,可减少PCB空间占用。部分FPGA开发板会集成I2C总线仲裁电路,支持多主机同时访问总线。 FPGA 开发板蜂鸣器用于状态提示与报警。

FPGA开发板在航空航天领域的应用有着严格的要求与独特的价值。在卫星通信系统中,开发板可用于实现卫星与地面站之间的数据传输与信号处理功能。由于太空中的环境复杂,信号传输面临诸多挑战,FPGA开发板凭借其高可靠性与可重构性,能够在恶劣环境下稳定工作。开发板可以实现复杂的编码调制算法,提高信号传输的效率与抗干扰能力;同时,在接收端进行精细的解调,确保数据的准确接收。在飞行器的导航系统中,开发板参与处理来自惯性导航传感器、卫星导航等设备的数据,通过复杂的算法融合这些数据,为飞行器提供精确的位置、速度与姿态信息,飞行器的安全飞行。此外,开发板的可重构特性使得在飞行器任务执行过程中,能够根据实际需求调整功能模块,适应不同的飞行任务与环境变化,为航空航天事业的发展提供可靠的技术。FPGA 开发板外设接口过压保护保障安全。浙江国产FPGA开发板工程师

FPGA 开发板散热设计保障芯片稳定运行。山东学习FPGA开发板平台

1.FPGA开发板的时钟模块作用时钟信号是FPGA数字逻辑设计的“脉搏”,开发板上的时钟模块通常由晶体振荡器、时钟缓冲器和时钟分配网络组成。晶体振荡器能提供高精度的固定频率信号,常见频率有25MHz、50MHz、100MHz等,部分板卡还会集成可配置的时钟发生器,支持通过软件调整输出频率,满足不同算法对时钟周期的需求。时钟缓冲器可将单一时钟信号复制为多路同步信号,分配给FPGA内部的不同逻辑模块,避免因信号延迟导致的时序偏差。在高速数据处理场景中,如图像处理或通信信号解调,时钟模块的稳定性直接影响数据采样精度和逻辑运算的同步性,因此部分开发板还会加入时钟抖动抑制电路,进一步降低信号噪声。山东学习FPGA开发板平台