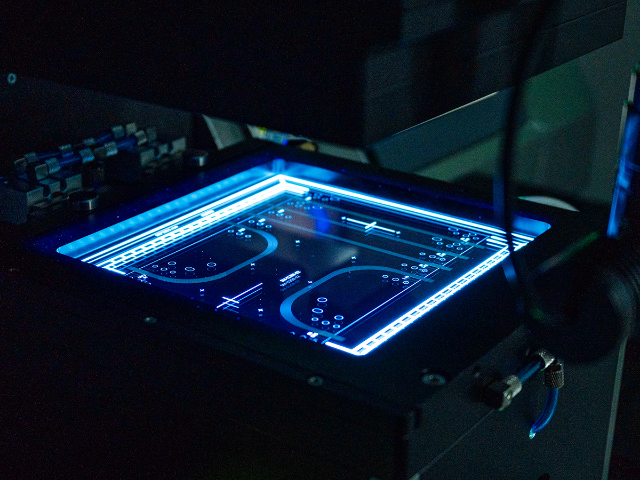

三维光子互连技术与多芯MT-FA光连接器的融合,正在重塑芯片级光通信的物理架构。传统电子互连受限于铜线传输的电阻损耗与电磁干扰,在3nm制程时代已难以满足AI芯片间T比特级数据传输需求。而三维光子互连通过垂直堆叠光子器件与波导结构,构建了立体化的光信号传输网络。这种架构突破二维平面布局的物理限制,使光子器件密度提升3-5倍,同时通过垂直耦合器实现层间光信号的无损传输。多芯MT-FA作为该体系的重要接口,采用42.5°端面研磨工艺与低损耗MT插芯,在800G/1.6T光模块中实现12-24通道的并行光连接。其V槽pitch公差控制在±0.3μm以内,配合紫外胶水OG198-54的精密粘接,确保多芯光纤的阵列精度达到亚微米级。实验数据显示,这种结构在2304通道并行传输时,单比特能耗可低至50fJ,较传统电子互连降低82%,而带宽密度突破5.3Tb/s/mm²,为AI训练集群的算力扩展提供了关键支撑。三维光子互连芯片凭借其高速、低耗、大带宽的优势。贵阳多芯MT-FA光组件支持的三维芯片架构

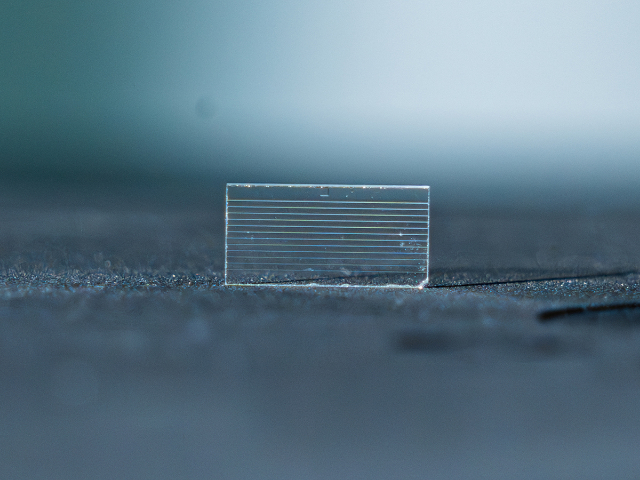

三维光子集成工艺对多芯MT-FA的制造精度提出了严苛要求,其重要挑战在于多物理场耦合下的工艺稳定性控制。在光纤阵列制备环节,需采用DISCO高精度切割机实现V槽边缘粗糙度小于50nm,配合精工Core-pitch检测仪将通道间距误差控制在±0.3μm以内。端面研磨工艺则需通过多段式抛光技术,使42.5°反射镜面的曲率半径偏差不超过0.5%,同时保持光纤凸出量一致性在±0.1μm范围内。在三维集成阶段,层间对准精度需达到亚微米级,这依赖于飞秒激光直写技术对耦合界面的精确修饰。通过优化光栅耦合器的周期参数,可使层间传输损耗降低至0.05dB/界面,配合低温共烧陶瓷中介层实现热膨胀系数匹配,确保在-40℃至85℃工作温度范围内耦合效率波动小于5%。实际测试数据显示,采用该工艺的12通道MT-FA组件在800Gbps速率下,连续工作72小时的误码率始终维持在10^-15量级,充分验证了三维集成工艺在高速光通信场景中的可靠性。这种技术演进不仅推动了光模块向1.6T及以上速率迈进,更为6G光子网络、量子通信等前沿领域提供了可扩展的集成平台。贵阳多芯MT-FA光组件支持的三维芯片架构三维光子互连芯片的喷砂法TGV工艺,提升玻璃基板加工效率。

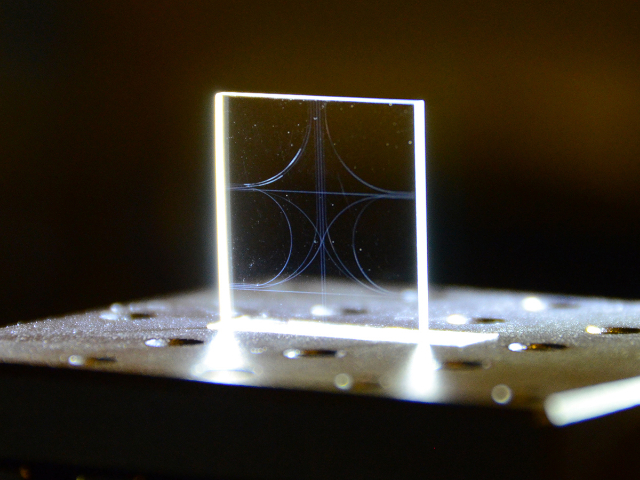

多芯MT-FA光组件的三维光子耦合方案是突破高速光通信系统带宽瓶颈的重要技术,其重要在于通过三维空间光路设计实现多芯光纤与光芯片的高效耦合。传统二维平面耦合受限于光芯片表面平整度与光纤阵列排布精度,导致耦合损耗随通道数增加呈指数级上升。而三维耦合方案通过在垂直于光芯片平面的方向引入微型反射镜阵列或棱镜结构,将水平传输的光模式转换为垂直方向耦合,使多芯光纤的纤芯与光芯片波导实现单独、低损耗的垂直对接。例如,采用5个三维微型反射镜组成的聚合物阵列,通过激光直写技术精确控制反射镜的曲面形貌与空间排布,可实现各通道平均耦合损耗低于4dB,工作波长带宽超过100纳米,且兼容CMOS工艺与波分复用技术。这种设计不仅解决了高密度通道间的串扰问题,还通过三维堆叠结构将光模块体积缩小40%以上,为800G/1.6T光模块的小型化提供了关键支撑。

三维光子互连技术通过电子与光子芯片的垂直堆叠,为MT-FA开辟了全新的应用维度。传统电互连在微米级铜线传输中面临能耗与频宽瓶颈,而三维光子架构将光通信收发器直接集成于芯片堆叠层,利用2304个微米级铜锡键合点构建光子立交桥,实现800Gb/s总带宽与5.3Tb/s/mm²的单位面积数据密度。在此架构中,MT-FA作为光信号进出芯片的关键接口,通过定制化端面角度(如8°至42.5°)与模斑转换设计,实现与三维光子层的高效耦合。例如,采用45°端面MT-FA可完成垂直光路耦合,减少光信号在层间传输的损耗;而集成Lens的FA模块则能优化光斑匹配,提升耦合效率。实验数据显示,三维光子互连架构下的MT-FA通道能耗可低至50fJ/bit,较传统方案降低70%,同时通过分布式回损检测技术,可实时监测FA内部微裂纹与光纤微弯,将产品失效率控制在0.3%以下。随着AI算力需求向Zettaflop级迈进,三维光子互连与MT-FA的深度融合将成为突破芯片间通信瓶颈的重要路径,推动光互连技术向更高密度、更低功耗的方向演进。三维光子互连芯片通过优化光路设计,减少信号串扰以提升传输质量。

从系统集成角度看,多芯MT-FA光组件的定制化能力进一步强化了三维芯片架构的灵活性。其支持端面角度、通道数量、保偏特性等参数的深度定制,可适配不同工艺节点的三维堆叠需求。例如,在逻辑堆叠逻辑(LOL)架构中,上层芯片可能采用5nm工艺实现高性能计算,下层芯片采用28nm工艺优化功耗,MT-FA组件可通过调整光纤阵列的pitch精度(误差<0.5μm)和偏振消光比(≥25dB),确保异构晶片间的光耦合效率超过95%。此外,其体积小、高密度的特性与三维芯片的紧凑设计高度契合,单个MT-FA组件可替代传统多个单芯连接器,将封装体积缩小40%以上,同时通过多芯并行传输降低布线复杂度,使系统级信号完整性(SI)提升20%。这种深度集成不仅简化了三维芯片的散热设计,还通过光信号的隔离特性减少了层间电磁干扰(EMI),为高带宽、低延迟的AI算力架构提供了物理层保障。随着三维芯片向单芯片集成万亿晶体管的目标演进,MT-FA光组件的技术迭代将直接决定其能否突破内存墙与互连墙的双重限制,成为未来异构集成系统的重要基础设施。三维光子互连芯片的可靠性测试持续开展,确保满足不同行业的应用标准。贵阳多芯MT-FA光组件支持的三维芯片架构

自动驾驶汽车测试中,三维光子互连芯片确保多摄像头数据的同步处理。贵阳多芯MT-FA光组件支持的三维芯片架构

从工艺实现层面看,多芯MT-FA的部署需与三维芯片制造流程深度协同。在芯片堆叠阶段,MT-FA的阵列排布精度需达到亚微米级,以确保与上层芯片光接口的精确对准。这一过程需借助高精度切割设备与重要间距测量技术,通过优化光纤阵列的端面研磨角度(8°~42.5°可调),实现与不同制程芯片的光路匹配。例如,在存储器与逻辑芯片的异构堆叠中,MT-FA组件可通过定制化通道数量(4/8/12芯可选)与保偏特性,满足高速缓存与计算单元间的低时延数据交互需求。同时,MT-FA的耐温特性(-25℃~+70℃工作范围)使其能够适应三维芯片封装的高密度热环境,配合200次以上的插拔耐久性,保障了系统长期运行的可靠性。这种部署模式不仅提升了三维芯片的集成度,更通过光互连替代部分电互连,将层间信号传输功耗降低了30%以上,为高算力场景下的能效优化提供了关键支撑。贵阳多芯MT-FA光组件支持的三维芯片架构

从工艺实现层面看,多芯MT-FA的部署需与三维芯片制造流程深度协同。在芯片堆叠阶段,MT-FA的阵列...

【详情】三维光子芯片与多芯MT-FA光连接方案的融合,正在重塑高速光通信系统的技术边界。传统光模块中,电信号...

【详情】三维光子互连技术与多芯MT-FA光纤连接的融合,正在重塑芯片级光通信的底层架构。传统电互连因电子迁移...

【详情】多芯MT-FA光组件作为三维光子芯片实现高密度光互连的重要器件,其技术特性与三维集成架构形成深度协同...

【详情】高性能多芯MT-FA光组件的三维集成方案通过突破传统二维平面布局的物理限制,实现了光信号传输密度与系...

【详情】多芯MT-FA光组件的三维光子耦合方案是突破高速光通信系统带宽瓶颈的重要技术,其重要在于通过三维空间...

【详情】高密度多芯MT-FA光组件的三维集成技术,是光通信领域突破传统二维封装物理极限的重要路径。该技术通过...

【详情】多芯MT-FA光组件三维芯片耦合技术作为光通信领域的前沿突破,其重要在于通过垂直堆叠与高精度互连实现...

【详情】三维光子芯片的研发正推动光互连技术向更高集成度与更低能耗方向突破。传统光通信系统依赖镜片、晶体等分立...

【详情】高密度多芯MT-FA光组件的三维集成芯片技术,是光通信领域突破传统物理限制的关键路径。该技术通过将多...

【详情】三维光子互连芯片的多芯MT-FA封装技术,是光通信与半导体封装交叉领域的前沿突破。该技术以多芯光纤阵...

【详情】三维光子芯片的集成化发展对光连接器提出了前所未有的技术挑战,而多芯MT-FA光连接器凭借其高密度、低...

【详情】