- 品牌

- 上海伟诺

- 型号

- 伟诺

- 适用行业

- 半导体

- 版本类型

- 网络版

- 语言版本

- 简体中文版

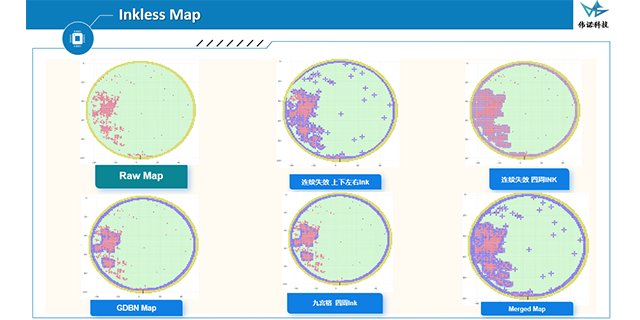

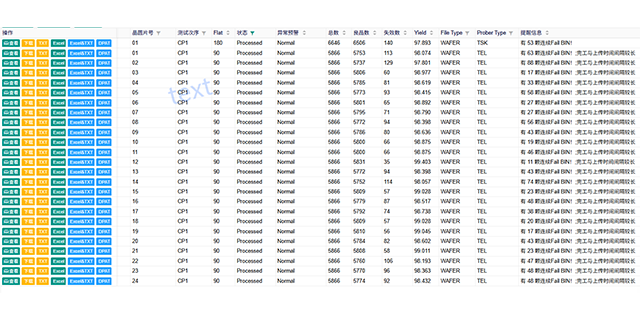

在半导体设计公司或封测厂面临多源测试数据难以统一管理的挑战时,YMS良率管理系统提供了一套端到端的解决方案。系统自动对接ETS88、93k、J750、Chroma、STS8200、TR6850等主流Tester平台,采集stdf、csv、xls、spd、jdf、log、zip、txt等多种格式原始数据,并完成重复性检测、缺失值识别与异常过滤,确保分析基础可靠。通过标准化数据库对数据统一分类,企业可从时间维度追踪良率趋势,或聚焦晶圆特定区域对比缺陷分布,快速定位工艺异常。结合WAT、CP与FT参数的联动分析,进一步揭示影响良率的根本原因。SYL与SBL的自动计算与卡控机制强化了过程质量防线,而灵活的报表工具支持按模板生成日报、周报、月报,并导出为PPT、Excel或PDF格式,满足跨层级决策需求。上海伟诺信息科技有限公司自2019年成立以来,持续打磨YMS系统,助力客户构建自主可控的良率管理能力。Mapping Over Ink处理系统输出结构化日志,完整记录处理过程满足质量追溯需求。湖南可视化PAT系统

企业在评估测封良率管理系统投入时,关注的是功能覆盖度与长期服务保障。YMS提供模块化配置,支持根据实际使用的Tester类型(如ETS364、Juno、AMIDA、CTA8280等)和数据格式(包括stdf、jdf、log等)灵活调整功能组合。系统不仅完成数据自动清洗与整合,还通过标准化数据库实现时间趋势、区域对比及缺陷聚类的多维分析。SYL与SBL的自动计算与阈值卡控,为封测过程设置动态质量防线。报价策略基于定制化程度与服务范围,确保企业在合理预算内获得高性价比解决方案。配套的售前咨询、售中方案优化与售后标准化服务,保障系统稳定运行与持续演进。上海伟诺信息科技有限公司以透明定价与完整服务体系,帮助客户实现良率管理的可持续提升。甘肃晶圆Mapping InklessMapping Over Ink处理严格遵循AECQ标准进行风险判定,确保车规级芯片可靠性。

因测试数据错误导致误判良率,可能引发不必要的重测或错误工艺调整,造成材料与时间双重浪费。YMS在数据入库前执行多层校验,自动剔除异常记录,确保进入分析环节的数据真实反映产品状态。例如,当某晶圆因通信中断产生部分缺失数据时,系统会标记该记录而非直接纳入统计,避免拉低整体良率。结合WAT、CP、FT参数的交叉验证,进一步排除孤立异常点。高质量数据输入使质量决策建立在可靠基础上,明显降低返工率和报废风险。这种前置质量控制机制,将成本节约从“事后补救”转向“事前预防”。上海伟诺信息科技有限公司通过严谨的数据治理逻辑,保障YMS输出结果的科学性与可执行性。

面对国产半导体制造对自主可控软件的迫切需求,良率管理系统成为打通数据孤岛、实现质量闭环的关键工具。系统自动采集ETS88、93k、J750、Chroma等主流Tester平台输出的stdf、csv、xls、log、spd、jdf、zip、txt等多种格式测试数据,通过内置算法识别重复项、缺失值并过滤异常记录,确保后续分析基于高可信度数据源。在标准化数据库支撑下,企业可从时间维度追踪良率趋势,或聚焦晶圆特定区域对比缺陷分布,快速定位工艺波动点。结合WAT、CP与FT参数的联动分析,进一步揭示影响良率的深层原因。SYL与SBL的自动计算与卡控机制,强化了过程质量防线。灵活的报表工具支持按模板生成日报、周报、月报,并导出为PPT、Excel或PDF格式,提升跨部门协同效率。上海伟诺信息科技有限公司自2019年成立以来,专注打造适配本土需求的YMS系统,助力构建中国半导体软件生态。Mapping Over Ink处理系统提供售前咨询与售后标准化服务,保障客户实施体验。

良率波动若不能及时干预,可能造成数百万级的产能损失。YMS系统通过自动化流程,即时采集并清洗来自多种测试平台的异构数据,构建高可信度分析基础。系统支持从宏观趋势到微观缺陷的穿透式分析,例如将某产品月度良率下降与特定封装线关联,并结合FT参数验证是否为打线偏移导致。SYL/SBL卡控机制设置动态阈值,在指标异常时自动预警,实现前置质量管控。多周期报表自动生成并支持多格式导出,使管理层能基于一致数据源快速决策。这种“实时感知—智能归因—主动干预”的能力,将良率管理从经验驱动升级为数据驱动。上海伟诺信息科技有限公司以“以信为本,以质取胜”为准则,持续打磨YMS的可靠性与实用性。Mapping Over Ink数据处理流程全程自动化运行,大幅减少人工复核的人为干预。湖南可视化PAT系统

Mapping Over Ink处理因数据分析自动化大幅提升效率,缩短封测周期时间。湖南可视化PAT系统

在半导体制造中,由于Fab制程的物理与化学特性,晶圆边缘的芯片(Edge Die)其失效率明显高于中心区域。这一现象主要源于几个关键因素:首先,在光刻、刻蚀、薄膜沉积等工艺中,晶圆边缘的反应气体流场、温度场及压力场分布不均,导致工艺一致性变差;其次,边缘区域更容易出现厚度不均、残留应力集中等问题;此外,光刻胶在边缘的涂覆均匀性也通常较差。这些因素共同导致边缘芯片的电气参数漂移、性能不稳定乃至早期失效风险急剧升高。因此,在晶圆测试(CP)的制造流程中,对电性测试图谱(Wafer Mapping)执行“去边”操作,便成为一项提升产品整体良率与可靠性的关键步骤。

上海伟诺信息科技有限公司Mapping Over Ink功能中的Margin Map功能提供多种算法与自定义圈数,满足客户快速高效低剔除边缘芯片,可以从根本上避免后续对这些潜在不良品进行不必要的封装和测试,从而直接节约成本,并确保出厂产品的质量与可靠性要求。湖南可视化PAT系统

上海伟诺信息科技有限公司在同行业领域中,一直处在一个不断锐意进取,不断制造创新的市场高度,多年以来致力于发展富有创新价值理念的产品标准,在上海市等地区的数码、电脑中始终保持良好的商业口碑,成绩让我们喜悦,但不会让我们止步,残酷的市场磨炼了我们坚强不屈的意志,和谐温馨的工作环境,富有营养的公司土壤滋养着我们不断开拓创新,勇于进取的无限潜力,携手大家一起走向共同辉煌的未来,回首过去,我们不会因为取得了一点点成绩而沾沾自喜,相反的是面对竞争越来越激烈的市场氛围,我们更要明确自己的不足,做好迎接新挑战的准备,要不畏困难,激流勇进,以一个更崭新的精神面貌迎接大家,共同走向辉煌回来!

- 可视化PAT平台 2026-04-26

- 安徽可视化GDBC系统定制 2026-04-26

- 江西可视化MappingOverInk处理软件 2026-04-26

- 天津可视化MappingOverInk处理解决方案 2026-04-26

- 天津自动化PAT工具 2026-04-25

- 北京MappingOverInk处理工具 2026-04-25

- 湖南自动化MappingOverInk处理服务商 2026-04-25

- 晶圆PAT解决方案 2026-04-25