芯片封装的散热设计:随着芯片集成度不断提高,功耗随之增加,散热问题愈发突出。良好的散热设计能确保芯片在正常温度范围内运行,避免因过热导致性能下降甚至损坏。中清航科在芯片封装过程中,高度重视散热设计,通过优化封装结构、选用高导热材料、增加散热鳍片等方式,有效提升封装产品的散热性能。针对高功耗芯片,公司还会采用先进的液冷散热封装技术,为客户解决散热难题,保障芯片长期稳定运行,尤其在数据中心、高性能计算等领域发挥重要作用。中清航科聚焦芯片封装,用创新结构设计,提升芯片抗振动冲击能力。上海半导体封装测试

在LED照明与显示技术不断革新的背景下,COB(ChiponBoard,板上芯片封装)技术凭借高集成度、均匀出光等优势,成为行业焦点。众多LED封装厂家围绕COB技术展开研发与实践,实现了多项关键突破。散热性能提升是COB技术突破的重要方向。传统封装中,热量积聚易导致光衰加速、寿命缩短。厂家通过改进基板材料,采用高导热陶瓷基板或金属基复合材料,大幅降低热阻;同时优化芯片布局与封装结构,构建高效散热通道,使COB模组的工作温度明显降低,有效提升了产品稳定性与使用寿命。国内封装厂芯片封装考验细节把控,中清航科以严苛标准,确保每颗芯片稳定运行。

芯片封装的基础概念:芯片封装,简单来说,是安装半导体集成电路芯片的外壳。它承担着安放、固定、密封芯片的重任,能有效保护芯片免受物理损伤以及空气中杂质的腐蚀。同时,芯片封装也是沟通芯片内部与外部电路的关键桥梁,芯片上的接点通过导线连接到封装外壳的引脚上,进而与印制板上的其他器件建立连接。中清航科深谙芯片封装的基础原理,凭借专业的技术团队,能为客户解读芯片封装在整个半导体产业链中的基础地位与关键作用,助力客户从源头理解相关业务。

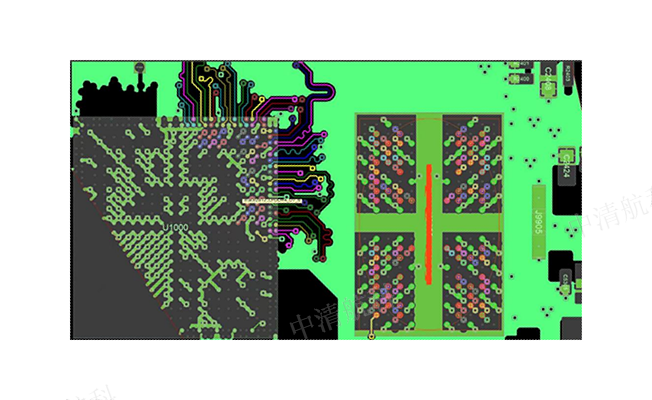

中清航科部署封装数字孪生系统,通过AI视觉检测实现微米级缺陷捕捉。在BGA植球工艺中,球径一致性控制±3μm,位置精度±5μm。智能校准系统使设备换线时间缩短至15分钟,产能利用率提升至90%。针对HBM内存堆叠需求,中清航科开发超薄芯片处理工艺。通过临时键合/解键合技术实现50μm超薄DRAM晶圆加工,4层堆叠厚度400μm。其TSV深宽比达10:1,阻抗控制在30mΩ以下,满足GDDR6X1TB/s带宽要求。中清航科可拉伸封装技术攻克可穿戴设备难题。采用蛇形铜导线与弹性体基底结合,使LED阵列在100%拉伸形变下保持导电功能。医疗级生物相容材料通过ISO10993认证,已用于动态心电图贴片量产。中清航科芯片封装技术,支持多引脚设计,满足芯片高集成度需求。

随着摩尔定律逼近物理极限,先进封装成为提升芯片性能的关键路径。中清航科在Fan-Out晶圆级封装(FOWLP)领域实现突破,通过重构晶圆级互连架构,使I/O密度提升40%,助力5G射频模块厚度缩减至0.3mm。其开发的激光解键合技术将良率稳定在99.2%以上,为毫米波通信设备提供可靠封装方案。面对异构集成需求激增,中清航科推出3DSiP立体封装平台。该方案采用TSV硅通孔技术与微凸点键合工艺,实现CPU、HBM内存及AI加速器的垂直堆叠。在数据中心GPU领域,其散热增强型封装结构使热阻降低35%,功率密度提升至8W/mm²,满足超算芯片的严苛要求。中清航科聚焦芯片封装,用仿真预判风险,缩短研发验证周期。半导体封装 焊线

中清航科专注芯片封装,通过材料革新让微型化与高效能兼得。上海半导体封装测试

面向CPO共封装光学,中清航科开发硅光芯片耦合平台。通过亚微米级主动对准系统,光纤-光栅耦合效率>85%,误码率<1E-12。单引擎集成8通道112GPAM4,功耗降低45%。中清航科微流控生物芯片封装通过ISO13485认证。采用PDMS-玻璃键合技术,实现5μm微通道密封。在PCR检测芯片中,温控精度±0.1℃,扩增效率提升20%。针对GaN器件高频特性,中清航科开发低寄生参数QFN封装。通过金线键合优化将电感降至0.2nH,支持120V/100A器件在6GHz频段工作。电源模块开关损耗减少30%。上海半导体封装测试