UFS 信号完整性之数据速率关联

数据速率与 UFS 信号完整性紧密相关。随着 UFS 技术发展,数据传输速率不断提升,对信号完整性要求愈发严苛。在高速率下,信号传输过程中的损耗、反射、串扰等问题更加突出。例如,UFS 4.0 相比 UFS 3.1 数据速率大幅提高,信号在传输线中传播时,高频分量更容易衰减,微小的信号完整性问题都可能导致大量数据传输错误。为适应高数据速率,需在硬件设计上采用更先进的工艺、材料,优化传输线结构,提升信号抗干扰能力;在测试环节,也需针对高速信号特点,制定更严格的测试标准和方法,保障 UFS 在高数据速率下维持良好信号完整性。 UFS 信号完整性测试之环境因素考量?高速接口UFS信号完整性测试时钟抖动测试

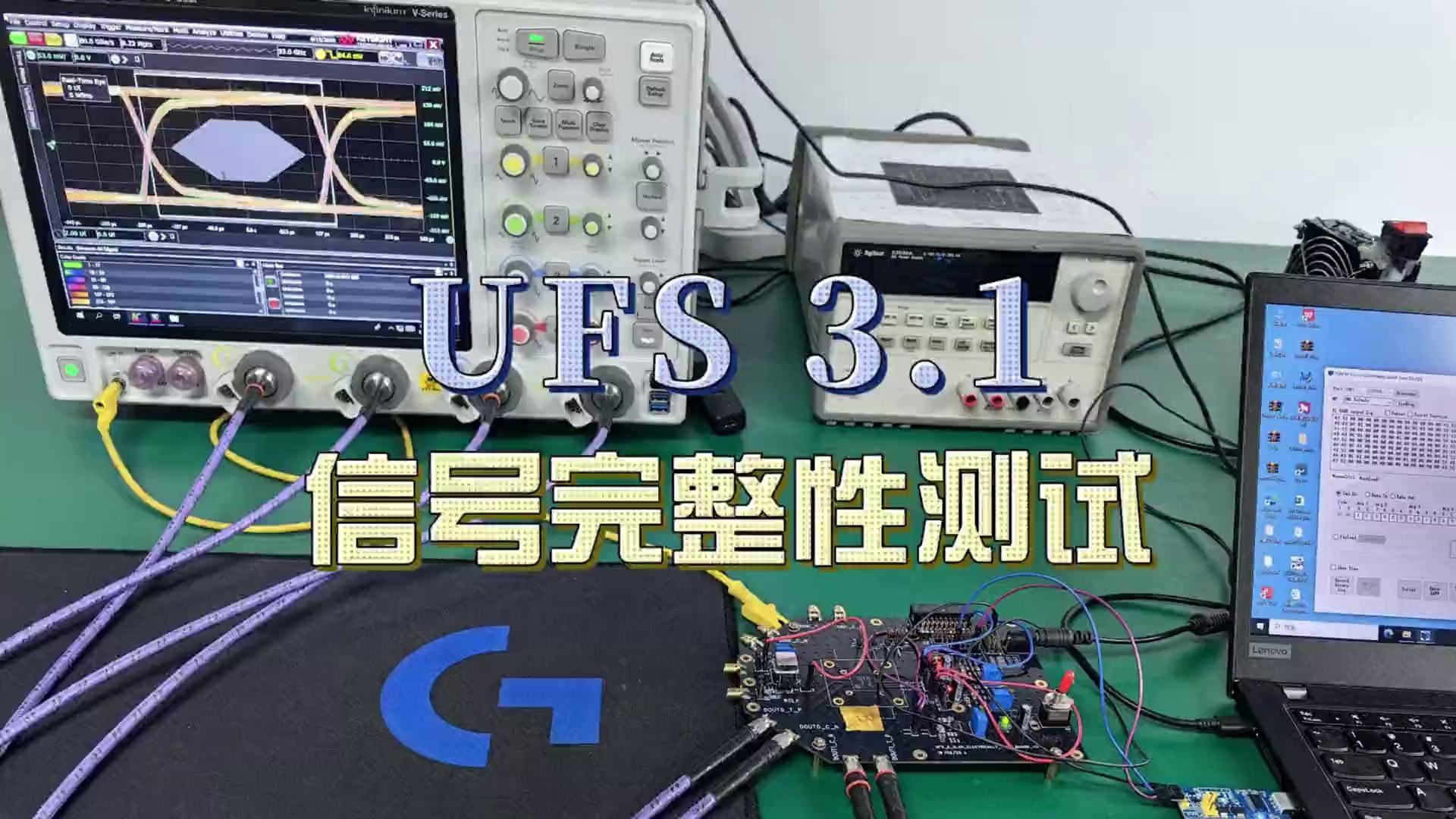

UFS信号完整性测试

UFS 信号完整性测试之 AI 辅助优化

在 UFS 信号完整性测试里,AI 技术正发挥关键作用。利用 AI 算法,能对大量测试数据进行深度挖掘与分析。比如,通过机器学习模型,可快速识别信号参数间的潜在关联,精细预测信号完整性问题。在测试过程中,AI 能依据实时信号状况,自动调整测试策略,优化测试流程。当发现信号抖动异常,AI 能迅速分析可能原因,如线路干扰、元件参数漂移等,并给出相应解决建议。借助 AI 辅助,不仅提升 UFS 信号完整性测试效率,还能更高效地保障信号传输的稳定性与可靠性,推动 UFS 技术不断优化。 物理层信号完整性测试(SI/PI)UFS信号完整性测试抖动测试UFS 信号完整性测试之多通道同步测试要点?

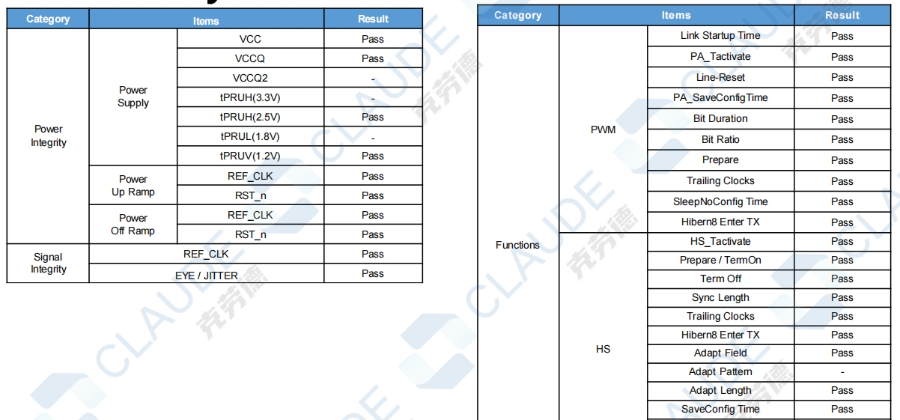

UFS 信号完整性之电源完整性关联

电源完整性与 UFS 信号完整性紧密相连。UFS 设备稳定工作依赖良好的电源供应。电源纹波过大,会在芯片内部产生噪声,干扰信号传输,影响信号的电压稳定性,导致信号电平波动,增加误码率。同时,电源分配网络(PDN)的阻抗特性也至关重要。在高频段,若 PDN 阻抗过高,会使电源电压出现较大压降,影响芯片正常工作,进而破坏信号完整性。例如,在设计 UFS 电源时,需使用大容量电容(如 10μF + 0.1μF)来降低电源纹波,构建低阻抗的 PDN,确保电源稳定,为 UFS 信号完整性创造良好的电源环境。

UFS 信号完整性与数据准确性

UFS 信号完整性直接关系到数据准确性。信号在传输中若发生反射、串扰、失真等问题,数据就可能出错。当信号完整性良好,数据能准确无误地从发射端传至接收端。比如在存储设备读取数据时,稳定的信号确保读取数据与原始存储数据一致。所以,保证 UFS 信号完整性,是实现数据准确传输与存储的重心,对设备数据处理可靠性意义重大。

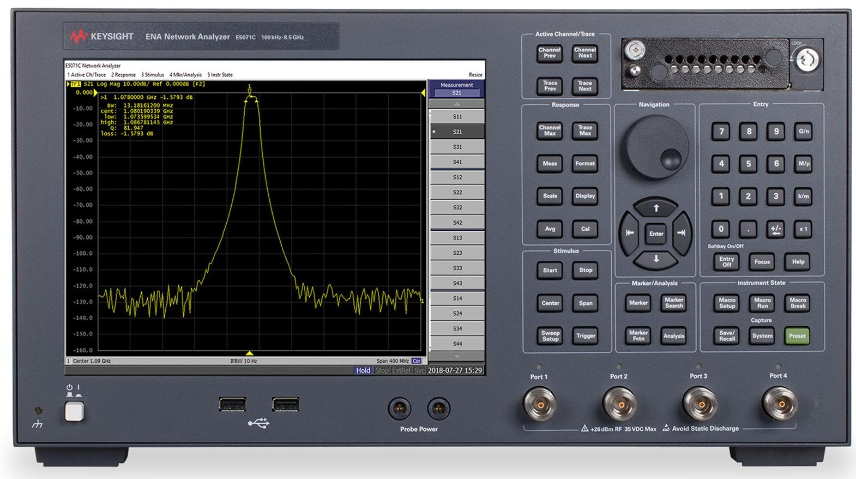

UFS 信号完整性测试之阻抗控制

阻抗控制是 UFS 信号完整性测试重点。传输线阻抗需匹配,否则信号反射严重,降低信号质量。通过 TDR(时域反射计)测量传输线阻抗,要求为 50Ω±5% 。若阻抗突变,会导致信号畸变,影响数据传输。在布线时,精心设计线路长度、宽度等,确保阻抗稳定。良好的阻抗控制能减少信号损耗,是 UFS 信号完整性测试与保障信号高效传输的关键环节。 UFS 信号完整性测试之信号完整性与行业标准遵循?

UFS 信号完整性测试之信号完整性与产品质量

UFS 信号完整性是产品质量重要指标。信号传输稳定、准确,产品性能才有保障。从生产环节的测试,到成品检验,信号完整性测试贯穿始终。若信号完整性不达标,产品可能出现各种问题,影响用户体验。严格把控 UFS 信号完整性测试,能提升产品质量,增强产品市场竞争力,树立良好品牌形象。

UFS 信号完整性测试之信号完整性与测试成本

UFS 信号完整性测试成本需合理控制。高精度测试设备、专业测试人员增加成本。但忽视信号完整性,产品质量问题会导致售后成本大增。在测试中,选择合适测试方案与工具,提高测试效率,降低成本。例如,用性价比高的测试仪器,满足测试精度要求。平衡信号完整性与测试成本,既能保证产品质量,又能控制企业运营成本。 UFS 信号完整性测试之信号完整性与数据加密的关系?高速接口UFS信号完整性测试时钟抖动测试

UFS 信号完整性测试之信号完整性与设备可靠性?高速接口UFS信号完整性测试时钟抖动测试

UFS 信号完整性测试之量子加密关联

随着量子加密技术发展,UFS 信号完整性测试与之产生关联。量子加密的安全性依赖于量子态的稳定性,而 UFS 信号传输质量会影响量子加密数据的存储与读取。若 UFS 信号完整性差,量子加密数据在存储过程中可能发生错误,导致失败。测试时,需在量子加密环境下评估 UFS 信号。一方面优化 UFS 信号传输,确保数据准确存储;另一方面,研究量子加密对 UFS 信号的特殊要求,如对信号噪声容限的更高标准。保障二者协同工作,既提升数据安全性,又保证 UFS 存储性能。 高速接口UFS信号完整性测试时钟抖动测试

UFS 信号完整性与传输线损耗 传输线损耗是影响 UFS 信号完整性的重要因素。在 UFS 数据传输过程中,信号沿传输线传播时,会因导体电阻、介质损耗等原因逐渐衰减。高频信号尤为明显,其在传输线中传播,能量不断被消耗,导致信号幅度降低、波形变形。例如,较长的 PCB 走线、低质量的连接器,都会加剧传输线损耗。为降低损耗对信号完整性的影响,一方面要选用低损耗的 PCB 板材,精心设计传输线参数,像控制合适的走线长度、线宽等;另一方面,可借助信号调理电路,对衰减的信号进行放大、整形。有效管控传输线损耗,是维持 UFS 信号完整性、保障高速数据可靠传输的关键举措。 UFS 信号完整性测试之...

- 软件测试UFS信号完整性测试信号眼图 2026-04-04

- 高速信号UFS信号完整性测试操作 2026-04-04

- 转接板UFS信号完整性测试示波器和探头治具 2026-04-04

- 通信UFS信号完整性测试检测 2026-04-04

- si信号完整性UFS信号完整性测试保证质量 2026-04-03

- 软件测试UFS信号完整性测试端口测试 2026-04-03

- 测试原理UFS信号完整性测试检测 2026-04-03

- 高速信号UFS信号完整性测试 2026-04-03

- 测试原理UFS信号完整性测试(SI/PI) 2026-04-03

- 夹具测试UFS信号完整性测试 2026-04-03

- si信号完整性UFS信号完整性测试物理层测试 2026-04-02

- 解决方案UFS信号完整性测试测试工具 2026-04-02

- 眼图测试UFS信号完整性测试插入损耗测试 2026-04-01

- 设备UFS信号完整性测试时钟抖动测试 2026-04-01

- 高速接口UFS信号完整性测试时钟抖动测试 2026-03-09

- 转接板UFS信号完整性测试M-PHY测试 2026-03-08

- 高速信号UFS信号完整性测试操作 04-04

- 广东解决方案PCIE3.0TX一致性测试方案 04-04

- 浙江测量LVDS发射端一致性测试 04-04

- 转接板UFS信号完整性测试示波器和探头治具 04-04

- 通信UFS信号完整性测试检测 04-04

- 重庆DDR测试LVDS发射端一致性测试 04-04

- 广东数字信号PCIE3.0TX一致性测试 04-03

- si信号完整性UFS信号完整性测试保证质量 04-03

- DDR测试USB3.0测试眼图测试 04-03

- 数字信号PCIE3.0TX一致性测试操作 04-03