- 品牌

- 云茂

- 型号

- 齐全

- 封装形式

- B***GA,CSP,QFP/PFP,MCM,SDIP,SOP/SOIC,PLCC,TSOP,TQFP,PQFP,SMD,DIP

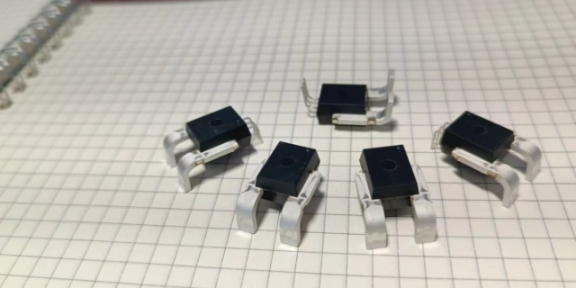

合封电子、芯片合封和SiP系统级封装经常被提及的概念。但它们是三种不同的技术,还是同一种技术的不同称呼?本文将帮助我们更好地理解它们的差异。合封电子与SiP系统级封装的定义,首先合封电子和芯片合封都是一个意思合封电子是一种将多个芯片(多样选择)或不同的功能的电子模块(LDO、充电芯片、射频芯片、mos管)封装在一起的定制化芯片,从而形成一个系统或者子系统。以实现更复杂、更高效的任务。云茂电子可定制组成方式包括CoC封装技术、SiP封装技术等。SiP 封装优势:封装面积增大,SiP在同一个封装种叠加两个或者多个芯片。吉林MEMS封装测试

3D SIP。3D封装和2.5D封装的主要区别在于:2.5D封装是在Interposer上进行布线和打孔,而3D封装是直接在芯片上打孔和布线,电气连接上下层芯片。3D集成目前在很大程度上特指通过3D TSV的集成。物理结构:所有芯片及无源器件都位于XY平面之上且芯片相互叠合,XY平面之上设有贯穿芯片的TSV,XY平面之下设有基板布线及过孔。电气连接:芯片采用TSV与RDL直接电连接。3D集成多适用于同类型芯片堆叠,将若干同类型芯片竖直叠放,并由贯穿芯片叠放的TSV相互连接而成,见下图。类似的芯片集成多用于存储器集成,如DRAM Stack和FLASH Stack。北京SIP封装供应商Sip这种创新性的系统级封装不只大幅降低了PCB的使用面积,同时减少了对外围器件的依赖。

此外,在电源、车载通讯方面也开始进行了 SiP 探索和开发实践。随着电子硬件不断演进,过去产品的成本随着电子硬件不断演进,性能优势面临发展瓶颈,而先进的半导体封装技术不只可以增加功能、提升产品价值,还有效降低成本。SiP 兼具低成本、低功耗、高性能、小型化和多元化的优势。2021 年,全球 SiP 市场规模约为 150 亿美元;预计 2021-2026 年,全球 SiP 市场年均复合增长率将在 5.8% 左右,到 2026 年市场规模将达到 199 亿美元左右。受益于人工智能、物联网、5G 等产业快速发展,预计未来 5 年,可穿戴智能设备、IoT 物联网设备将会是推动全球 SiP 市场增长的重要动力。目前全世界封装的产值只占集成电路总值的 10%,当 SiP 技术被封装企业掌握后,产业格局就要开始调整,封装业的产值将会出现一个跳跃式的提高。SiP 在应用终端产品领域(智能手表、TWS、手机、穿戴式产品、5G 模组、AI 模组、智能汽车)的爆发点也将愈来愈近。

失效分析三步骤 X射线检测(3D X–ray):透过失效分析当中的X–ray检测,我们可以深入确认模块是否有封装异常,并且找出异常组件的位置。 材料表面元素分析(XPS):接着,利用XPS针对微米等级的模块表面进行更细微的元素分析,以此探究模块出现电阻值偏高、电性异常、植球脱球及镀膜脱层等现象是否来自于制程的氧化或污染。 傅立叶红外线光谱仪(FTIR):如明确查找到污染物目标,则可再接续使用FTIR进行有机污染物的鉴定,定义出问题根源究竟是来自哪一个阶段,以此找出正确解决方案。SiP系统级封装技术将处理芯片、存储芯片、被动元件、连接器、天线等多功能器件整合在同一基板上。

SiP模块可靠度及失效分析,由于内部线路和基板之间的复杂链接,当模块出现问题时,分析微米级组件的异常变得特别具有挑战性,尤其是在电性测试期间,其他部件的导电性会影响测定结果。而且某些异常污染可能光只有几奈米的厚度,如:氧化或微侵蚀,使用一般的光学或电子显微镜根本无法发现。为了将制程问题降至较低,云茂电子在SiP模块失效分析领域持续强化分析能力,以X射线检测(3D X–ray)、材料表面元素分析(XPS) 及傅立叶红外线光谱仪(FTIR)等三大品管仪器找出解决之道。 SIP是从封装的立场出发,对不同芯片进行并排或叠加的封装方式,实现一定功能的单个标准封装件。吉林MEMS封装测试

SiP系统级封装作为一种集成封装技术,在满足多种先进应用需求方面发挥着关键作用。吉林MEMS封装测试

包装,主要目的是保证运输过程中的产品安全,及长期存放时的产品可靠性。对包装材料的强度、重量、温湿度特性、抗静电性能都有一定的要求。主要材料有Tray盘,抗静电袋,干燥剂、湿度卡,纸箱等。包装完毕后,直接入库或按照要求装箱后直接发货给客户。倒装焊封装工艺工序介绍,焊盘再分布,为了增加引线间距并满足倒装焊工艺的要求,需要对芯片的引线进行再分布。制作凸点,焊盘再分布完成之后,需要在芯片上的焊盘添加凸点,焊料凸点制作技术可采用电镀法、化学镀法、蒸发法、置球法和焊膏印尽4法。目前仍以电镀法较为普遍,其次是焊膏印刷法。吉林MEMS封装测试

PoP封装技术有以下几个有点:1)存储器件和逻辑器件可以单独地进行测试或替换,保障了良品率;2)双层POP封装节省了基板面积, 更大的纵向空间允许更多层的封装;3)可以沿PCB的纵向将Dram,DdramSram,Flash,和 微处理器进行混合装联;4)对于不同厂家的芯片, 提供了设计灵活性,可以简单地混合装联在一起以满足客户的需求,降低了设计的复杂性和成本;5)目前该技术可以取得在垂直方向进行层芯片外部叠加装联;6)顶底层器件叠层组装的电器连接,实现了更快的数据传输速率,可以应对逻辑器件和存储器件之间的高速互联。系统级封装(SiP)技术是通过将多个裸片(Die)及无源器件整合在单个封装体内...

- 辽宁SIP封装方式 2024-11-07

- 浙江系统级封装方案 2024-11-07

- 重庆IPM封装测试 2024-11-06

- 安徽WLCSP封装价位 2024-11-05

- 南通系统级封装价格 2024-11-05

- 陕西陶瓷封装价位 2024-11-04

- 四川COB封装方式 2024-11-04

- 深圳WLCSP封装厂商 2024-11-04

- 广东SIP封装厂家 2024-11-03

- 广西COB封装技术 2024-11-01

- 北京BGA封装方式 2024-10-27

- 深圳BGA封装价格 2024-10-26

- 湖北COB封装流程 2024-10-26

- 贵州MEMS封装供应 2024-10-26

- 广西芯片封装定制价格 2024-10-25

- 浙江COB封装服务商 2024-10-23

- 浙江系统级封装方案 11-07

- 北京新能源汽车随车充产品方案策划 11-07

- 福建半导体MES系统定制价格 11-07

- 江苏PCBA板特种封装厂商 11-07

- 芯片特种封装测试 11-06

- 陕西专业特种封装价格 11-06

- 广东WMS系统市场价格 11-06

- 重庆IPM封装测试 11-06

- 北京特种封装 11-06

- 甘肃专业特种封装市价 11-06