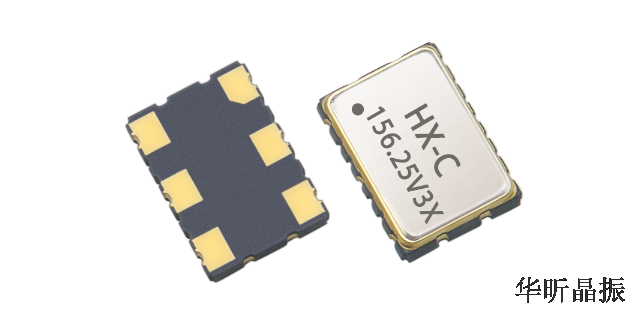

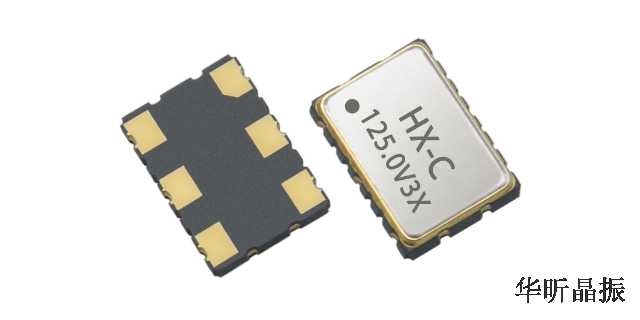

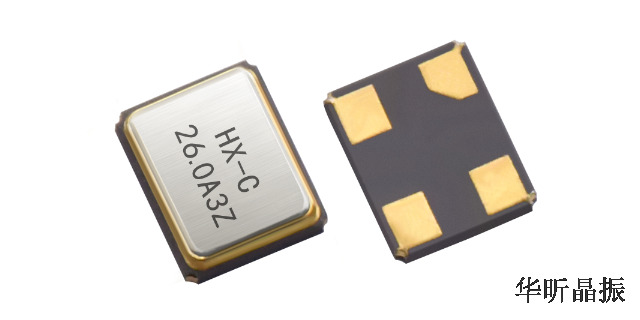

- 品牌

- 华昕

- 型号

- 7S025000VEL

- 频率特性

- 高频

- 封装材料

- 金属

- 外形

- 贴片式

- 标称频率

- 156.25

- 调整频差

- 156.25

- 基准温度

- -40~+85

- 负载谐振电阻

- 0.005

- 温度范围

- -40~+85

- 产地

- 中国

- 厂家

- 华昕

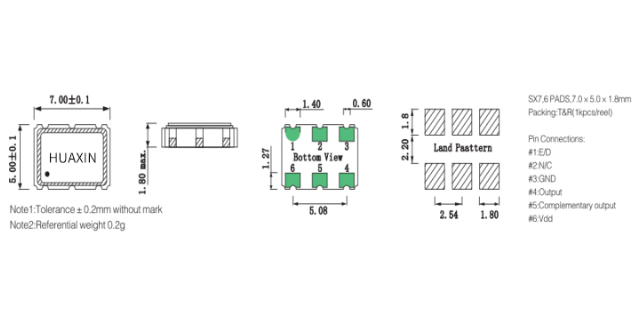

- 封装尺寸

- 7.0*5.0

- 类型

- 差分晶振

- 输出模式

- LVDS

- 电压

- 3.3V

差分晶振与微处理器的连接方式

差分晶振,作为一种高性能的振荡器,以其低电平、低抖动和低功耗等特性,在现代电子设备中发挥着至关重要的作用。它

能够输出差分信号,使用两种相位完全相反的信号来消除共模噪声,从而极大地提高系统的性能。微处理器,作为计算机系统的关键,负责执行指令、处理数据以及控制其他部件的运行。其由大规模集成电路组成,包括寄存器堆、运算器、时序控制电路等,能够完成取指令、执行指令以及与外界存储器和逻辑部件交换信息等操作。差分晶振与微处理器的连接,主要是通过差分信号线与微处理器的时钟输入端口进行连接。

差分晶振输出的差分信号,经过适当的电路处理,可以直接接入微处理器的时钟系统,为微处理器提供稳定、精确的时钟信号。在连接过程中,需要注意差分信号的平衡性和对称性,以确保信号传输的稳定性和可靠性。同时,还需要考虑差分晶振的工作电压、频率范围等参数与微处理器的兼容性,以避免因不匹配而导致的性能下降或损坏。

此外,为了进一步提高系统的稳定性和抗干扰能力,还可以在差分晶振与微处理器之间加入滤波电路和隔离器件,以减小噪声干扰和电磁辐射的影响。 差分晶振如何与FPGA连接?吉林差分晶振分类

差分晶振,即输出为差分信号的晶振。其主要的应用场景包括以下几个方面:

时钟振荡电路:差分晶振在计算机、通信设备和其他电子设备中的时钟振荡电路中发挥着重要作用。它能产生准确的时间基准和频率信号,确保系统运行的稳定性和准确性。

数据通信:在数据通信中,差分晶振被用于时钟恢复和数据同步电路中。这种应用有助于确保数据传输的准确性和可靠性,为现代通信技术的发展提供了重要支持。

无线通信系统:差分晶振在无线通信系统中也扮演着关键角色。它被用于频率合成器和局部振荡器,产生稳定的射频信号,从而保证了无线通信的稳定性和可靠性。

测试和测量设备:在测试和测量设备中,差分晶振被用于时钟、计数器、频率计等部分,以确保测试结果的准确性和稳定性。

差分晶振的主要优势在于其强大的抗干扰能力、对参考电平完整性要求的弱化、强抑制串扰和EMI能力,以及功耗小、速率高、不受温度、电压波动影响等特点。这使得差分晶振在需要精确时间同步和频率控制的场合中表现出色,如通信、计算机等领域。此外,差分晶振还具有宽温范围与长寿命的特点,能在恶劣的电磁环境中保持良好的性能。差分晶振几乎覆盖了所有需要精确时间同步和频率控制的领域。 SG5032VAN差分晶振差分晶振的相位延迟如何?

差分晶振输出为差分信号,通过使用两种相位完全相反的信号来消除共模噪声,从而实现更高性能的系统。在选择适合差分晶振的PCB布局时,需要注意以下几点。

首先,差分晶振的抗干扰能力强,对参考电平(地平面或电源平面)完整性要求较弱,因此在布局时,应尽量将差分晶振放置在远离可能产生噪声的区域,如大电流线路或高频线路。

其次,差分晶振抑制串扰、EMI能力强,因此在布局时,应避免差分晶振的差分线对与其他信号线对平行走线,以减少电磁干扰。

再者,差分晶振的功耗小、速率高、不受温度、电压波动的影响,因此在布局时,应确保差分晶振的供电稳定,且差分线对的长度应尽量相等,以保证差分信号的传输质量。此外,差分信号使用两根导线或PCB走线,第二根导线或走线提供了电流的回路。因此,在布局时,应确保差分晶振的差分线对具有足够的空间进行布线,避免线路交叉或过于接近。

差分晶振的布局还需要考虑其与其他元器件的连接。应尽量缩短差分线对与其他元器件的连接线路,以减少信号传输的延迟和损耗。

选择适合差分晶振的PCB布局需要考虑多个因素,包括噪声、电磁干扰、供电稳定性、线路长度和连接等。

差分晶振的相位噪声分析

差分晶振,作为一种高性能的振荡器,广泛应用于通信、雷达、测试测量等领域。其相位噪声特性是衡量其性能的重要指标之一。相位噪声描述了振荡器输出频率的稳定性,对通信系统的性能有着直接的影响。

差分晶振的相位噪声通常较低,这得益于其独特的设计和工作原理。差分晶振采用差分输出,能够有效抑制共模噪声,提高信号的抗干扰能力。此外,差分晶振的电路结构和工作模式也有助于降低相位噪声。

在实际应用中,差分晶振的相位噪声表现优异。其稳定的输出频率和较低的相位噪声使得通信系统能够更准确地传输信息,提高了系统的可靠性和稳定性。同时,差分晶振的相位噪声特性也使其成为高精度测试测量设备的理想选择。

然而,差分晶振的相位噪声并非完美无缺。在实际应用中,还需要根据具体需求选择合适的差分晶振,并进行适当的电路设计和优化,以获得比较好的相位噪声性能。

综上所述,差分晶振的相位噪声表现优异,适用于对频率稳定性要求较高的应用场景。通过合理的电路设计和优化,可以进一步提高其相位噪声性能,满足更为严格的应用需求。 差分晶振的振动方向对性能有何影响?

差分晶振的振动方向,即其谐振时产生的机械振动方向,对其性能具有明显影响。

首先,振动方向决定了差分晶振的频率稳定性。晶振的频率稳定性取决于其谐振质量块在振动过程中的位移和受力情况。当振动方向与晶振的设计方向一致时,谐振质量块能够在比较和的状态下进行振动,从而减少能量损失,提高频率稳定性。反之,如果振动方向与设计方向不一致,可能会导致谐振质量块在振动过程中受到额外的阻力或干扰,从而降低频率稳定性。

其次,振动方向还会影响差分晶振的相位噪声。相位噪声是衡量晶振性能的重要指标之一,它反映了晶振输出信号的稳定度和纯净度。当振动方向与晶振设计方向一致时,谐振质量块的振动更为规则和稳定,这有助于减少相位噪声的产生。而振动方向与设计方向不一致时,可能导致谐振质量块的振动变得不规则,进而增加相位噪声。

此外,振动方向还会影响差分晶振的寿命和可靠性。长时间的振动可能导致晶振内部的机械结构发生磨损或疲劳,从而影响其性能和寿命。如果振动方向与设计方向一致,可以减少这种磨损和疲劳,提高晶振的寿命和可靠性。

差分晶振的振动方向对其性能具有重要影响。因此,在选择和使用差分晶振时,应充分考虑其振动方向与设计方向的匹配程度。 差分晶振的焊接温度和时间如何控制?SG5032VAN差分晶振

差分晶振的电源电压范围是多少?吉林差分晶振分类

差分晶振与FPGA的连接方式及应用

差分晶振以其独特的差分信号输出方式,有效地消除了共模噪声,实现了高性能的系统运行。而FPGA,作为现场可编程门阵列,具备高度的灵活性和可配置性,使得其在各种应用场景中都能发挥出色性能。那么,差分晶振如何与FPGA进行连接呢?

首先,差分晶振的输出为差分信号,因此在与FPGA连接时,需要确保FPGA的输入端口能够接收差分信号。这通常意味着需要使用FPGA上的差分输入接收器(DifferentialInputReceiver)来实现与差分晶振的连接。连接时,差分晶振的正负两根信号线应分别接入FPGA的差分输入接收器的对应引脚。这种连接方式可以有效地保证差分信号的完整性,避免因信号传输过程中的噪声干扰而影响系统的性能。

在连接过程中,还需要注意差分晶振的工作电压和频率等参数与FPGA的兼容性。确保差分晶振的电源电压、工作频率等参数在FPGA的接受范围内,以确保连接的稳定性和可靠性。差分晶振与FPGA的连接,不仅使得系统能够获得稳定、准确的时钟信号,而且还可以通过FPGA的编程能力,实现对时钟信号的灵活处理和控制。这使得差分晶振与FPGA的组合在各种需要高性能时钟源的应用场景中,如通信、数据处理等领域,具有广泛的应用前景。

吉林差分晶振分类

它们的主要功能是为系统提供稳定的时钟信号,确保设备的正常运行。 差分晶振的可靠性主要取决于其材料和设计。高质量的材料能够抵抗恶劣的工作环境,如高温、低温、高湿度等,从而保证晶振的稳定运行。此外,先进的设计也可以提高差分晶振的可靠性。例如,一些差分晶振采用了抗震设计,能够抵抗外部冲击和振动,避免因机械应力引起的故障。 在差分晶振的生产过程中,质量控制也是保证可靠性的重要环节。通过严格的生产流程和检测标准,可以确保每一个出厂的差分晶振都达到了预定的性能标准。此外,长期的老化测试和环境适应性测试也是评估差分晶振可靠性的重要手段。 除了材料和设计,差分晶振的可靠性还与其应用领域和...

- 300M差分晶振电压 2024-12-05

- 山东差分晶振规格书 2024-12-05

- SG5032VAN差分晶振推荐 2024-11-28

- 南昌120M差分晶振 2024-11-27

- 上海差分晶振怎么收费 2024-11-25

- 吉林差分晶振分类 2024-11-17

- 高稳差分晶振哪个好 2024-11-09

- 重庆差分晶振怎么收费 2024-10-29

- 3225差分晶振料号 2024-10-28

- 合肥低功耗差分晶振 2024-10-22

- 山西差分晶振应用领域 2024-10-12

- 陕西差分晶振供应商 2024-10-08

- 高稳差分晶振 2024-10-07

- 芜湖差分晶振温度系数 2024-10-05

- 148.5MHz差分晶振电压 2024-10-04

- 山东差分晶振输出模式 2024-10-02

- 厦门无源晶振30MHZ 12-22

- 杭州无源晶振26MHZ 12-22

- 北京无源晶振排名 12-22

- 无锡厂家无源晶振 12-21

- 广州无源晶振频率 12-21

- 圆柱无源晶振生产商 12-21

- 安徽无源晶振27MHZ 12-21

- 4M石英晶振分类 12-20

- 22.1184M石英晶振生产商 12-20

- 石家庄无源晶振厂家 12-20