- 品牌

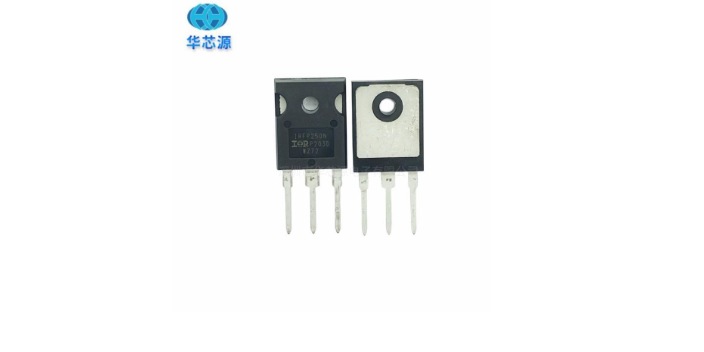

- TI,Infineon,ST 、ADI、NXP、,Maxim

- 型号

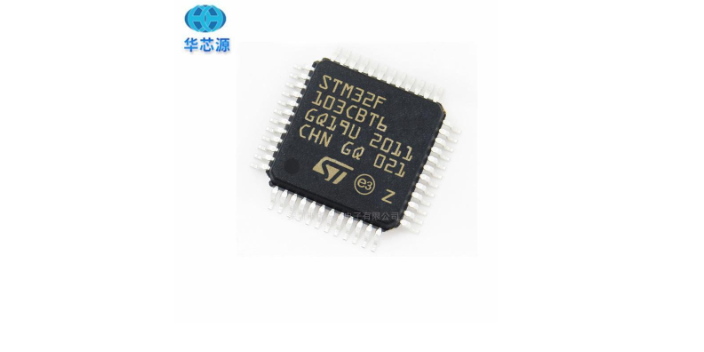

- MAX13487EESA+T、STM32F103VCT6

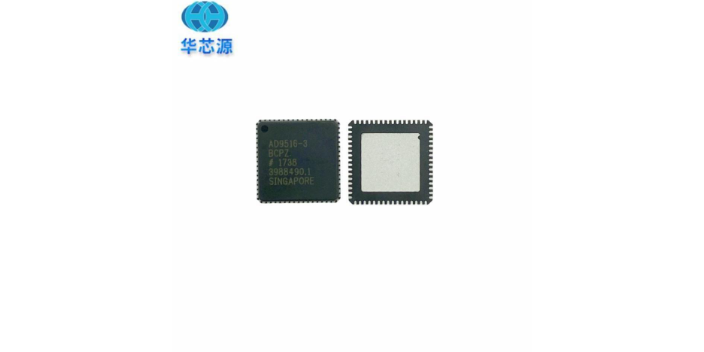

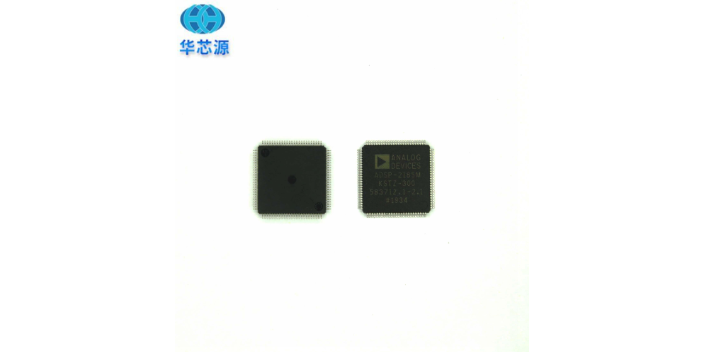

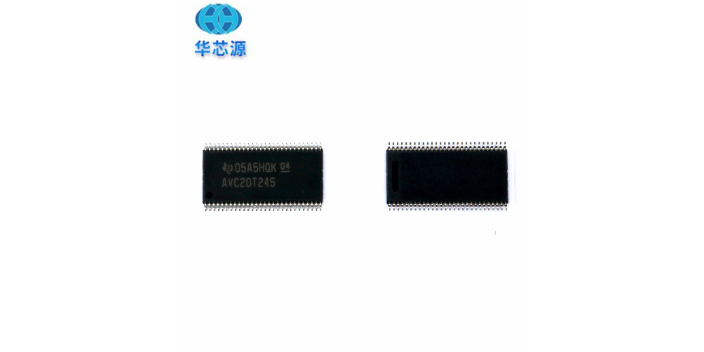

- 封装形式

- SOP/SOIC

- 导电类型

- 双极型,单极型

- 封装外形

- 扁平型

- 集成度

- 小规模(<50),中规模(50~100),大规模(100~10000)

- 批号

- 22+

- 应用领域

- 3C数码,安防设备,测量仪器,电工电气,机械设备,家用电器,医疗电子,网络通信,汽车电子,照明电子,智能家居,可穿戴设备

- 数量

- 9563

- 封装

- SOP

- 2881240033

- 厂家

- Maxim

随着AI智能硬件的快速爆发,IC设计行业迎来新的发展机遇,一批国内IC设计企业凭借准确的赛道布局实现业绩大幅增长。过去三年,在AIoT、智能终端等领域的带动下,瑞芯微、炬芯科技、全志科技等企业纷纷突破,实现营收和利润的双增长。瑞芯微从2023年的亏损状态,发展到2025年归母净利润突破10亿元,同比增长超70%,主要原因在于其深耕AIoT领域,布局多算力AIoT SoC芯片平台,满足端侧小模型部署需求。炬芯科技则凭借存内计算技术的端侧AI音频芯片,抓住高级智能音箱增长红利,2025年净利润同比增幅高达91.40%,彰显了AI赛道对IC设计企业的带动作用。车规级 IC 芯片需满足宽温与高可靠性要求,是自动驾驶和车载系统的关键部件。TDA8190

IC芯片的主要参数是衡量芯片性能和适用场景的关键,不同参数决定了芯片的工作能力、稳定性和功耗水平,掌握芯片的主要参数,能够帮助我们合理选型,确保芯片在设备中稳定工作。IC芯片的关键参数主要包括工作电压、工作频率、功耗、集成度、引脚数量、工作温度范围、传输速率等。工作电压是芯片正常工作所需的电压,不同芯片的工作电压不同,常见的有3.3V、5V等,电压过高或过低都会导致芯片损坏;工作频率决定了芯片的运算速度和信号处理能力,频率越高,芯片的处理速度越快,适用于对性能要求高的场景;功耗分为静态功耗和动态功耗,静态功耗是芯片待机时的功耗,动态功耗是芯片工作时的功耗,低功耗芯片适用于电池供电的便携式设备;集成度指芯片上集成的晶体管数量,集成度越高,芯片的功能越复杂;工作温度范围则决定了芯片的适用环境,工业级芯片的工作温度范围更广,适用于恶劣环境。PDTC115TT可编程 IC 芯片(FPGA)支持现场编程,灵活适配不同场景的功能需求。

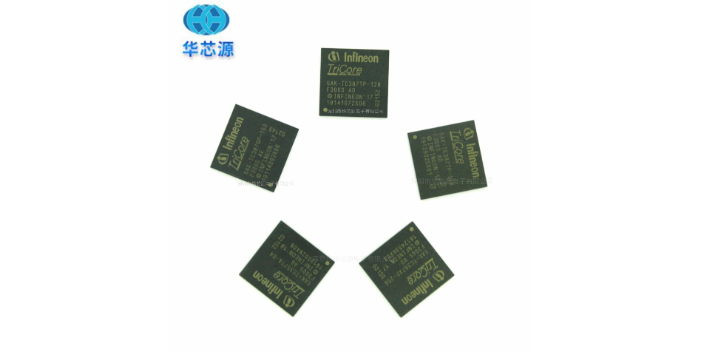

IC芯片的封装技术是芯片制造的重要环节,封装不仅能够保护芯片内部的电路和晶体管,防止外界环境(如灰尘、湿度、温度)对芯片造成损坏,还能提供芯片与外部设备的连接接口,实现信号和电能的传输。IC芯片的封装形式多样,不同的封装形式适用于不同的应用场景,根据引脚数量、体积、散热性能等,可分为插件式封装和贴片式封装两大类。插件式封装(如DIP封装)引脚较长,便于手工焊接,适用于原型制作、小型设备和对体积要求不高的场景;贴片式封装(如SOP、QFP、BGA)体积小、引脚密集,适用于高密度、小型化的电子设备,如手机、平板电脑、智能穿戴设备等。其中,BGA封装(球栅阵列封装)引脚以球形焊点的形式分布在芯片底部,具有引脚数量多、散热性能好、电气性能优越等优势,广泛应用于高级芯片,如CPU、GPU、FPGA等。随着芯片集成度的不断提高,封装技术也在不断升级,出现了SiP(系统级封装)、CoWoS(芯片级封装)等先进封装技术,能够将多个芯片集成在一个封装体内,实现更高的集成度和性能。

在 IC 芯片选购中,价格是影响采购决策的重要因素之一,尤其是对于批量采购的企业,细微的价格差异都可能带来明显的成本节省。华芯源凭借与品牌厂商的深度合作、规模化采购优势以及高效的运营体系,在价格方面形成了明显竞争力,让选购者能以更实惠的价格获得质优 IC 芯片,提升采购性价比。华芯源与恩智浦、德州仪器、意法半导体等品牌厂商建立了长期战略合作关系,作为这些品牌的主要分销商,其采购量远高于普通供应商,因此能获得厂商给予的阶梯式价格优惠 —— 采购量越大,单价越低。这种规模化采购优势,让华芯源能够将部分利润让渡给选购者,提供更具竞争力的终端报价。比如,某型号的 TI 运算放大器,普通供应商的报价为 15 元 / 颗,而通过华芯源批量采购 1000 颗以上,单价可降至 12 元 / 颗,这一项就能为企业节省 3000 元采购成本。存储类 IC 芯片为数据保存与读取提供了稳定可靠的硬件支撑。

IC 芯片作为电子设备的 “大脑”,其质量直接决定了终端产品的性能与安全,一旦采购到劣质或翻新芯片,不止会导致产品故障、维修成本增加,甚至可能引发安全事故。因此,质量管控是 IC 芯片选购过程中的重要关注点,而华芯源构建的全流程质量管控体系,为选购者筑牢了信任基石,让每一次采购都安心可靠。华芯源的质量管控从源头开始 —— 所有代理的 IC 芯片均来自品牌厂商或其授权的一级分销商,每一批货品都附带完整的采购凭证、质量认证文件(如 RoHS 认证、CE 认证、MIL 认证等)。在与品牌厂商合作前,华芯源会对其生产资质、质量体系进行严格审核,只选择通过 ISO9001 质量管理体系认证、具备稳定产能与良好口碑的企业建立合作关系,从源头上杜绝 “三无产品” 与翻新芯片流入供应链。从消费电子到工业设备,IC 芯片的应用已经渗透到各个行业。NVTFS5116PLTAG

IC 芯片的集成度分级涵盖 SSI、MSI、LSI 等,目前已发展至 ULSI 超大规模阶段。TDA8190

IC 芯片的制程工艺以晶体管栅极长度为衡量标准,从微米级向纳米级持续突破,是芯片性能提升的主要路径。制程演进的主要逻辑是通过缩小晶体管尺寸,在单位面积内集成更多晶体管,实现更高算力与更低功耗。20 世纪 90 年代以来,制程工艺从 0.5μm 逐步推进至 7nm、5nm,3nm 制程已实现量产,2nm 及以下制程处于研发阶段。制程突破依赖光刻技术的升级,从深紫外(DUV)到极紫外(EUV)光刻的跨越,实现了纳米级精度的电路图案转移。然而,随着制程逼近物理极限(如量子隧穿效应),传统摩尔定律面临挑战:一方面,研发成本呈指数级增长,单条先进制程生产线投资超百亿美元;另一方面,功耗密度问题凸显,晶体管漏电风险增加。为此,行业开始转向 Chiplet、3D IC 等先进封装技术,通过 “异构集成” 实现性能提升,开辟制程演进的新路径。TDA8190

- 江门数字转换IC芯片封装 2026-04-24

- TLV62568PDRLR 2026-04-24

- 四川存储器IC芯片丝印 2026-04-24

- SN74HC32DR 2026-04-24

- MAX4490AUK+T IC 2026-04-24

- DS2482S-100+T&R 2026-04-24

- ADM9690AR 2026-04-24

- TDA8190 2026-04-24

- IRFR2905ZPBF 2026-04-24

- D222K33Y5PL6UJ5R 2026-04-24

- 陕西存储器IC芯片价格 2026-04-24

- SC16IS752IPW 2026-04-24