刻蚀也可以分成有图形刻蚀和无图形刻蚀。有图形刻蚀采用掩蔽层(有图形的光刻胶)来定义要刻蚀掉的表面材料区域,只有硅片上被选择的这一部分在刻蚀过程中刻掉。有图形刻蚀可用来在硅片上制作多种不同的特征图形,包括栅、金属互连线、通孔、接触孔和沟槽。无图形刻蚀、反刻或剥离是在整个硅片没有掩模的情况下进行的,这种刻蚀工艺用于剥离掩模层。反刻是在想要把某一层膜的总的厚度减小时采用的(如当平坦化硅片表面时需要减小形貌特征)。广东省科学院半导体研究所。晶圆不同点刻蚀速率不同的情况称为非均匀性(或者称为微负载),通常以百分比表示。广州半导体材料刻蚀公司

相比刻蚀用单晶硅材料,芯片用单晶硅材料是芯片等终端产品的原材料,市场更为广阔,国产替代的需求也十分旺盛。SEMI的统计显示,2018年全球半导体制造材料市场规模为322.38亿美元,其中硅材料的市场规模达到121.24亿美元,占比高达37.61%。刻蚀用单晶硅材料和芯片用单晶硅材料在制造环节上有诸多相似之处:积累的固液共存界面控制技术、热场尺寸优化工艺、多晶硅投料优化等工艺技术已经达到国际先进水平,为进入新赛道提供了产业技术和经验的支撑。重庆深硅刻蚀材料刻蚀加工工厂ICP刻蚀设备能够进行(氮化镓)、(氮化硅)、(氧化硅)、(铝镓氮)等半导体材料进行刻蚀。

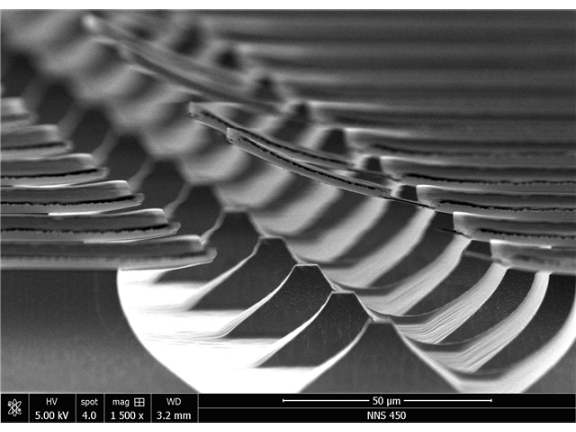

反应离子刻蚀(RIE)是当前常用技术路径,属于物理和化学混合刻蚀。在传统的反应离子刻蚀机中,进入反应室的气体会被分解电离为等离子体,等离子体由反应正离子、自由基、反应原子等组成。反应正离子会轰击硅片表面形成物理刻蚀,同时被轰击的硅片表面化学活性被提高,之后硅片会与自由基和反应原子形成化学刻蚀。这个过程中由于离子轰击带有方向性,RIE技术具有较好的各向异性。目前先进集成电路制造技术中用于刻蚀关键层的刻蚀方法是高密度等离子体刻蚀技术。传统的RIE系统难以使刻蚀物质进入高深宽比图形中并将残余生成物从中排出,因此不能满足0.25μm以下尺寸的加工要求,解决办法是增加等离子体的密度。高密度等离子体刻蚀技术主要分为电子回旋加速振荡(ECR)、电容或电感耦合等离子体(CCP/ICP)、双等离子体源等。

刻蚀技术(etchingtechnique),是在半导体工艺,按照掩模图形或设计要求对半导体衬底表面或表面覆盖薄膜进行选择性腐蚀或剥离的技术。刻蚀技术不仅是半导体器件和集成电路的基本制造工艺,而且还应用于薄膜电路、印刷电路和其他微细图形的加工。刻蚀还可分为湿法刻蚀和干法刻蚀。普通的刻蚀过程大致如下:先在表面涂敷一层光致抗蚀剂,然后透过掩模对抗蚀剂层进行选择性曝光,由于抗蚀剂层的已曝光部分和未曝光部分在显影液中溶解速度不同,经过显影后在衬底表面留下了抗蚀剂图形,以此为掩模就可对衬底表面进行选择性腐蚀。如果衬底表面存在介质或金属层,则选择腐蚀以后,图形就转移到介质或金属层上。刻蚀成了通过溶液、反应离子或其它机械方式来剥离、去除材料的一种统称。

二氧化硅湿法刻蚀:较普通的刻蚀层是热氧化形成的二氧化硅。基本的刻蚀剂是氢氟酸,它有刻蚀二氧化硅而不伤及硅的优点。然而,饱和浓度的氢氟酸在室温下的刻蚀速率约为300A/s。这个速率对于一个要求控制的工艺来说太快了。在实际中,氢氟酸与水或氟化铵及水混合。以氟化铵来缓冲加速刻蚀速率的氢离子的产生。这种刻蚀溶液称为缓冲氧化物刻蚀或BOE。针对特定的氧化层厚度,他们以不同的浓度混合来达到合理的刻蚀时间。一些BOE公式包括一个湿化剂用以减小刻蚀表面的张力,以使其均匀地进入更小的开孔区。干法刻蚀优点是:细线条操作安全,易实现自动化,无化学废液,处理过程未引入污染,洁净度高。四川Si材料刻蚀价格

氮化镓材料的刻蚀需要使用氧化硅作为掩膜来刻蚀,而氧化硅的刻蚀需要使用Cr充当硬掩模。广州半导体材料刻蚀公司

理想情况下,晶圆所有点的刻蚀速率都一致(均匀)。晶圆不同点刻蚀速率不同的情况称为非均匀性(或者称为微负载),通常以百分比表示。减少非均匀性和微负载是刻蚀的重要目标。应用材料公司一直以来不断开发具有成本效益的创新解决方案,来应对不断变化的蚀刻难题。这些难题可能源自于器件尺寸的不断缩小;所用材料的变化(例如高k薄膜或多孔较低k介电薄膜);器件架构多样化(例如FinFET和三维NAND晶体管);以及新的封装方式(例如硅穿孔(TSV)技术)。广州半导体材料刻蚀公司

广东省科学院半导体研究所位于长兴路363号,交通便利,环境优美,是一家服务型企业。广东省半导体所是一家****企业,一直“以人为本,服务于社会”的经营理念;“诚守信誉,持续发展”的质量方针。以满足顾客要求为己任;以顾客永远满意为标准;以保持行业优先为目标,提供***的微纳加工技术服务,真空镀膜技术服务,紫外光刻技术服务,材料刻蚀技术服务。广东省半导体所顺应时代发展和市场需求,通过**技术,力图保证高规格高质量的微纳加工技术服务,真空镀膜技术服务,紫外光刻技术服务,材料刻蚀技术服务。