多芯MT-FA光组件作为三维光子互连技术的重要载体,通过精密的多芯光纤阵列设计,实现了光信号在微米级空间内的高效并行传输。其重要优势在于将多根单模/多模光纤以阵列形式集成于MT插芯中,配合45°或8°~42.5°的定制化端面研磨工艺,形成全反射光路,使光信号在芯片间传输时的插入损耗可低至0.35dB,回波损耗超过60dB。这种设计不仅突破了传统电子互连的带宽瓶颈,更通过三维堆叠技术将光子器件与电子芯片直接集成,例如在800G/1.6T光模块中,MT-FA组件可承载2304条并行光通道,单位面积数据密度达5.3Tb/s/mm²,相比铜线互连的能效提升超90%。其应用场景已从数据中心扩展至AI训练集群,在400G/800G光模块中,MT-FA通过保偏光纤阵列与硅光芯片的耦合,实现了80通道并行传输下的总带宽800Gb/s,单比特能耗只50fJ,为高密度计算提供了低延迟、高可靠性的光互连解决方案。三维光子互连芯片通过垂直堆叠设计,实现了前所未有的集成度,极大提升了芯片的整体性能。石家庄高密度多芯MT-FA光组件三维集成芯片

从系统集成角度看,多芯MT-FA光组件的定制化能力进一步强化了三维芯片架构的灵活性。其支持端面角度、通道数量、保偏特性等参数的深度定制,可适配不同工艺节点的三维堆叠需求。例如,在逻辑堆叠逻辑(LOL)架构中,上层芯片可能采用5nm工艺实现高性能计算,下层芯片采用28nm工艺优化功耗,MT-FA组件可通过调整光纤阵列的pitch精度(误差<0.5μm)和偏振消光比(≥25dB),确保异构晶片间的光耦合效率超过95%。此外,其体积小、高密度的特性与三维芯片的紧凑设计高度契合,单个MT-FA组件可替代传统多个单芯连接器,将封装体积缩小40%以上,同时通过多芯并行传输降低布线复杂度,使系统级信号完整性(SI)提升20%。这种深度集成不仅简化了三维芯片的散热设计,还通过光信号的隔离特性减少了层间电磁干扰(EMI),为高带宽、低延迟的AI算力架构提供了物理层保障。随着三维芯片向单芯片集成万亿晶体管的目标演进,MT-FA光组件的技术迭代将直接决定其能否突破内存墙与互连墙的双重限制,成为未来异构集成系统的重要基础设施。昆明高密度多芯MT-FA光组件三维集成三维集成技术使得不同层次的芯片层可以紧密堆叠在一起,提高了芯片的集成度和性能。

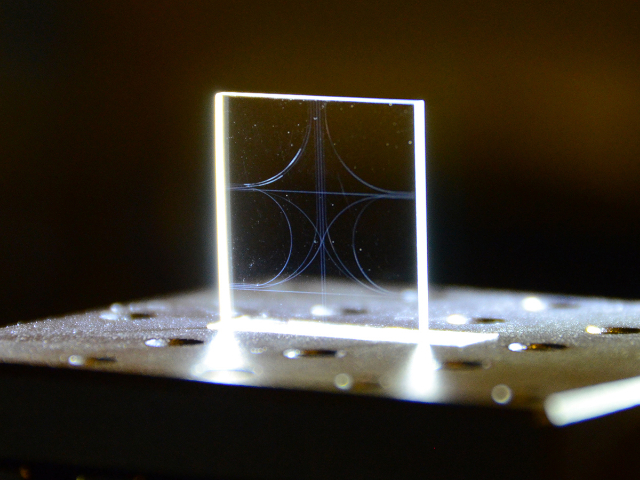

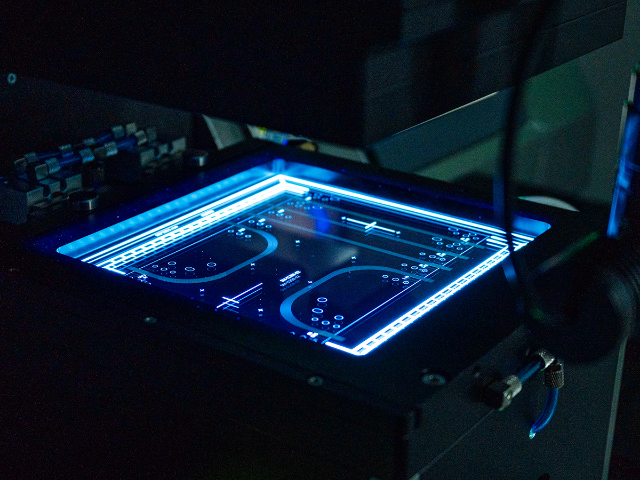

三维光子互连技术与多芯MT-FA光纤连接的融合,正在重塑芯片级光通信的底层架构。传统电互连因电子迁移导致的信号衰减和热损耗问题,在芯片制程逼近物理极限时愈发突出,而三维光子互连通过垂直堆叠的光波导结构,将光子器件与电子芯片直接集成,形成立体光子立交桥。这种设计不仅突破了二维平面布局的密度瓶颈,更通过微纳加工技术实现光信号在三维空间的高效传输。例如,采用铜锡热压键合工艺的2304个互连点阵列,在15微米间距下实现了114.9兆帕的剪切强度与10飞法的较低电容,确保了光子与电子信号的无损转换。多芯MT-FA光纤连接器作为关键接口,其42.5度端面研磨技术配合低损耗MT插芯,使单根光纤阵列可承载800Gbps的并行传输,通道均匀性误差控制在±0.5微米以内。这种设计在数据中心场景中展现出明显优势:当处理AI大模型训练产生的海量数据时,三维光子互连架构可将芯片间通信带宽提升至5.3Tbps/mm²,单比特能耗降低至50飞焦,较传统铜互连方案能效提升80%以上。

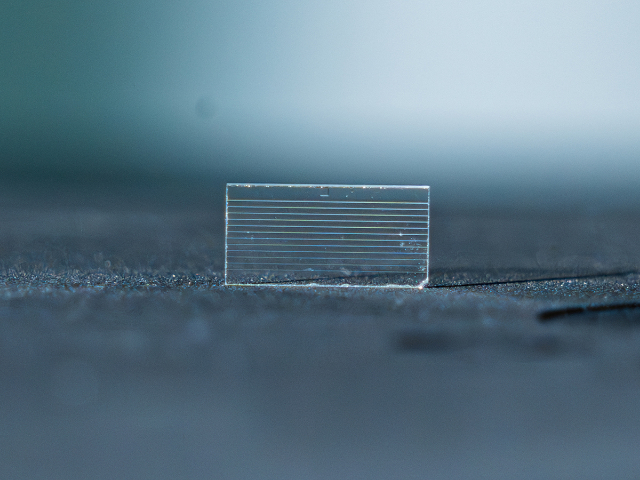

标准化进程的推进,需解决三维多芯MT-FA在材料、工艺与测试环节的技术协同难题。在材料层面,全石英基板与耐高温环氧树脂的复合应用,使光连接组件能适应-40℃至85℃的宽温工作环境,同时降低热膨胀系数差异导致的应力开裂风险。工艺方面,高精度研磨技术将光纤端面角度控制在42.5°±0.5°范围内,配合低损耗MT插芯的镀膜处理,使反射率优于-55dB,满足高速信号传输的抗干扰需求。测试标准则聚焦于多通道同步监测,通过引入光学频域反射计(OFDR),可实时检测48芯通道的插损、回损及偏振依赖损耗(PDL),确保每一路光信号的传输质量。当前,行业正推动建立覆盖设计、制造、验收的全链条标准体系,例如规定三维MT-FA的垂直堆叠层间对齐误差需小于1μm,以避免通道间串扰。这些标准的实施,将加速光模块从400G向1.6T及更高速率的迭代,同时推动三维光子芯片在超级计算机、6G通信等领域的规模化应用。三维光子互连芯片的喷砂法TGV工艺,提升玻璃基板加工效率。

从技术实现层面看,多芯MT-FA光组件的集成需攻克三大重要挑战:其一,高精度制造工艺要求光纤阵列的通道间距误差控制在±0.5μm以内,以确保与TSV孔径的精确对齐;其二,低插损特性需通过特殊研磨工艺实现,典型产品插入损耗≤0.35dB,回波损耗≥60dB,满足AI算力场景下长时间高负载运行的稳定性需求;其三,热应力管理要求组件材料与硅基板的热膨胀系数匹配度极高,避免因温度波动导致的层间剥离。实际应用中,该组件已成功应用于1.6T光模块的3D封装,通过将光引擎与电芯片垂直堆叠,使单模块封装体积缩小40%,同时支持800G至1.6T速率的无缝升级。在AI服务器背板互联场景下,MT-FA组件可实现每平方毫米10万通道的光互连密度,较传统方案提升2个数量级。这种技术突破不仅推动了三维芯片向更高集成度演进,更为下一代光计算架构提供了基础支撑,预示着光互连技术将成为突破内存墙功耗墙的重要驱动力。数据中心升级中,三维光子互连芯片可有效解决传统电互连带宽瓶颈问题。石家庄高密度多芯MT-FA光组件三维集成芯片

在高性能计算领域,三维光子互连芯片可以加速CPU、GPU等处理器之间的数据传输和协同工作。石家庄高密度多芯MT-FA光组件三维集成芯片

高密度多芯MT-FA光组件的三维集成芯片技术,是光通信领域突破传统物理限制的关键路径。该技术通过将多芯光纤阵列(MT-FA)与三维集成工艺深度融合,在垂直方向上堆叠光路层、信号处理层及控制电路层,实现了光信号传输与电学功能的立体协同。以400G/800G光模块为例,MT-FA组件通过42.5°精密研磨工艺形成端面全反射结构,配合低损耗MT插芯与亚微米级V槽定位技术,使多芯光纤的通道间距公差控制在±0.5μm以内,从而在单芯片内集成12至24路并行光通道。这种设计不仅将传统二维布局的布线密度提升3倍以上,更通过三维堆叠缩短了层间互连距离,使信号传输延迟降低40%,功耗减少25%。在AI算力集群中,该技术可支持单模块800Gbps的传输速率,满足大模型训练时每秒PB级数据交互的需求,同时其紧凑结构使光模块体积缩小60%,为数据中心高密度部署提供了物理基础。石家庄高密度多芯MT-FA光组件三维集成芯片

高密度多芯MT-FA光组件的三维集成方案,是应对AI算力爆发式增长背景下光通信系统升级需求的重要技术...

【详情】多芯MT-FA光组件在三维芯片架构中扮演着连接物理层与数据传输层的重要角色。三维芯片通过硅通孔(TS...

【详情】从技术实现层面看,多芯MT-FA光组件的集成需攻克三大重要挑战:其一,高精度制造工艺要求光纤阵列的通...

【详情】三维光子集成工艺对多芯MT-FA的制造精度提出了严苛要求,其重要挑战在于多物理场耦合下的工艺稳定性控...

【详情】多芯MT-FA光模块在三维光子互连系统中的创新应用,正推动光通信向超高速、低功耗方向演进。传统光模块...

【详情】从制造工艺层面看,多芯MT-FA光耦合器的突破源于材料科学与精密工程的深度融合。其重要部件MT插芯采...

【详情】三维光子集成多芯MT-FA光耦合方案是应对下一代数据中心与AI算力网络带宽瓶颈的重要技术突破。随着8...

【详情】三维光子互连技术与多芯MT-FA光连接器的融合,正在重塑芯片级光通信的物理架构。传统电子互连受限于铜...

【详情】三维光子芯片的研发正推动光互连技术向更高集成度与更低能耗方向突破。传统光通信系统依赖镜片、晶体等分立...

【详情】该标准的演进正推动光组件与芯片异质集成技术的深度融合。在制造工艺维度,三维互连标准明确要求MT-FA...

【详情】三维光子芯片多芯MT-FA架构的技术突破,本质上解决了高算力场景下存储墙与通信墙的双重约束。在AI大...

【详情】高性能多芯MT-FA光组件的三维集成方案通过突破传统二维平面布局的物理限制,实现了光信号传输密度与系...

【详情】