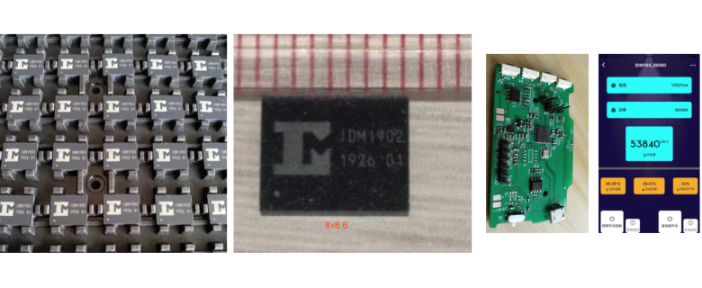

- 品牌

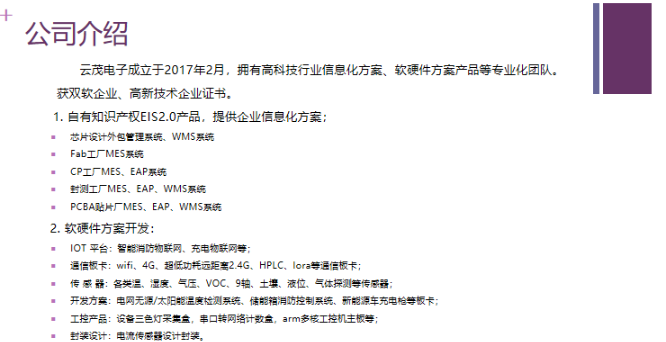

- 云茂

- 型号

- 齐全

- 封装形式

- B***GA,CSP,QFP/PFP,MCM,SDIP,SOP/SOIC,PLCC,TSOP,TQFP,PQFP,SMD,DIP

3D SIP。3D封装和2.5D封装的主要区别在于:2.5D封装是在Interposer上进行布线和打孔,而3D封装是直接在芯片上打孔和布线,电气连接上下层芯片。3D集成目前在很大程度上特指通过3D TSV的集成。物理结构:所有芯片及无源器件都位于XY平面之上且芯片相互叠合,XY平面之上设有贯穿芯片的TSV,XY平面之下设有基板布线及过孔。电气连接:芯片采用TSV与RDL直接电连接。3D集成多适用于同类型芯片堆叠,将若干同类型芯片竖直叠放,并由贯穿芯片叠放的TSV相互连接而成,见下图。类似的芯片集成多用于存储器集成,如DRAM Stack和FLASH Stack。SiP封装技术采取多种裸芯片或模块进行排列组装。重庆模组封装行价

SiP具有以下优势:降低成本 – 通常伴随着小型化,降低成本是一个受欢迎的副作用,尽管在某些情况下SiP是有限的。当对大批量组件应用规模经济时,成本节约开始显现,但只限于此。其他可能影响成本的因素包括装配成本、PCB设计成本和离散 BOM(物料清单)开销,这些因素都会受到很大影响,具体取决于系统。良率和可制造性 – 作为一个不断发展的概念,如果有效地利用SiP专业知识,从模塑料选择,基板选择和热机械建模,可制造性和产量可以较大程度上提高。重庆模组封装行价汽车汽车电子是 SiP 的重要应用场景。

与MCM相比,SiP一个侧重点在系统,能够完成单独的系统功能。除此之外,SiP是一种集成概念,而非固定的封装结构,它可以是2D封装结构、2.5D封装结构及3D封装结构。可以根据需要采用不同的芯片排列方式和不同的内部互联技术搭配,从而实现不同的系统功能。一个典型的SiP封装芯片如图所示。采用SiP封装的芯片结构图SiP封装可以有效解决芯片工艺不同和材料不同带来的集成问题,使设计和工艺制程具有较好的灵活性。与此同时,采用SiP封装的芯片集成度高,能减少芯片的重复封装,降低布局与排线的难度,缩短研发周期。

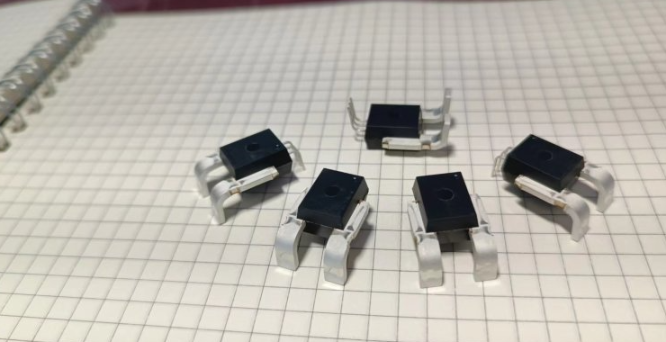

合封芯片的功能,性能提升,合封芯片:通过将多个芯片或模块封装在一起,合封芯片可以明显提高数据处理速度和效率。由于芯片之间的连接更紧密,数据传输速度更快,从而提高了整体性能。稳定性增强,合封芯片:由于多个芯片共享一些共同的功能模块,以及更紧密的集成方式,合封芯片可以减少故障率。功耗降低、开发简单,合封芯片:由于多个芯片共享一些共同的功能模块,以及更紧密的集成方式,云茂电子可以降低整个系统的功耗。此外,通过优化内部连接和布局,可以进一步降低功耗。防抄袭,多个芯片和元器件模块等合封在一起,就算被采购,也无法模仿抄袭。不同的芯片,排列方式,与不同内部结合技术搭配,使SiP 的封装形态产生多样化的组合。

3D主要有三种类型:埋置型、有源基板型、叠层型。其中叠层型是 当前普遍采用的封装形式。叠层型是在2D基础上,把多个裸芯片、封装芯片、多芯片组件甚至圆片进行垂直互连,构成立体叠层封装。可以通过三种方法实现:叠层裸芯片封装、封装堆叠直连和嵌入式3D封装。业界认定3D封装是扩展SiP应用的较佳方案,其中叠层裸芯片、封装堆叠、硅通孔互连等都是当前和将来3D封装的主流技术。并排放置(平面封装)的 SiP 是一种传统的多芯片模块封装形式,其中使用了引线键合或倒装芯片键合技术。SiP技术路线表明,越来越多的半导体芯片和封装将彼此堆叠,以实现更深层次的3D封装。重庆模组封装行价

SiP封装基板具有薄形化、高密度、高精度等技术特点。重庆模组封装行价

合封电子的功能,性能提升,合封电子:通过将多个芯片或模块封装在一起,云茂电子可以明显提高数据处理速度和效率。由于芯片之间的连接更紧密,数据传输速度更快,从而提高了整体性能。稳定性增强,合封电子:由于多个芯片共享一些共同的功能模块,以及更紧密的集成方式,云茂电子可以减少故障率。功耗降低、开发简单,合封电子:由于多个芯片共享一些共同的功能模块,以及更紧密的集成方式,云茂电子可以降低整个系统的功耗。此外,通过优化内部连接和布局,可以进一步降低功耗。防抄袭,多个芯片和元器件模块等合封在一起,就算被采购,也无法模仿抄袭。重庆模组封装行价

SiP系统级封装需求主要包括以下几个方面:1、稳定的力控制:在固晶过程中,需要对芯片施加一定的压力以确保其与基板之间的良好连接。然而,过大的压力可能导致芯片损坏,而过小的压力则可能导致连接不良。因此,固晶设备需要具备稳定的力控制能力,以确保施加在芯片上的压力恰到好处。2、温度场及变形的控制:在固晶过程中,温度的变化和基板的变形都可能影响芯片的位置和连接质量。因此,固晶设备需要具备对温度场和基板变形的控制能力,以确保在整个固晶过程中温度和变形的稳定。Sip系统级封装通过将多个裸片(Die)和无源器件融合在单个封装体内,实现了集成电路封装的创新突破。COB封装方案电子封装sip和sop的区别,在电...

- 山西MEMS封装供应商 2024-11-12

- 北京COB封装哪家好 2024-11-08

- 辽宁SIP封装方式 2024-11-07

- 浙江系统级封装方案 2024-11-07

- 重庆IPM封装测试 2024-11-06

- 安徽WLCSP封装价位 2024-11-05

- 南通系统级封装价格 2024-11-05

- 陕西陶瓷封装价位 2024-11-04

- 四川COB封装方式 2024-11-04

- 深圳WLCSP封装厂商 2024-11-04

- 广东COB封装工艺 2024-10-30

- 湖北半导体芯片封装厂商 2024-10-28

- 北京BGA封装方式 2024-10-27

- 深圳BGA封装价格 2024-10-26

- 湖北COB封装流程 2024-10-26

- 贵州MEMS封装供应 2024-10-26

- 山西MEMS封装供应商 11-12

- 深圳高压开关柜无源测温产品方案一站式服务 11-11

- 天津专业特种封装流程 11-11

- 江苏防震特种封装精选厂家 11-11

- 河南封测工厂WMS系统市价 11-11

- 浙江专业电子产品方案行价 11-11

- 智能硬件产品方案厂商 11-11

- 浙江电子手表产品方案 11-10

- 北京智能硬件产品方案服务商 11-10

- 陕西智能硬件产品方案 11-10